什么是射频集成电路设计?

出处:维库电子市场网 发布于:2023-12-05 17:00:22

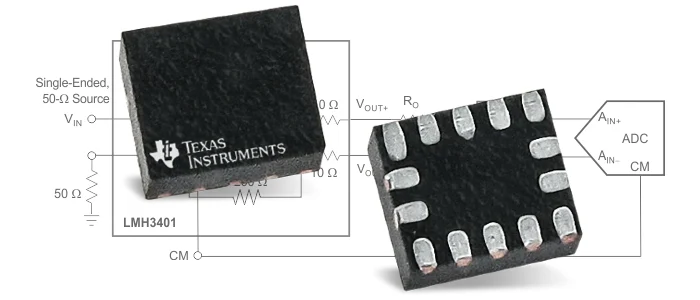

RF IC 设计与模拟 IC 设计的利基领域非常相似,通常是一种需要一种或多种 EDA 工具辅助的定制流程。RF IC 设计的部分性在于,寄生效应和封装特性对 RF 电路的性能具有一阶影响。因此,RF IC 设计通常是一个迭代过程,涉及在整个 IC 设计过程中广泛使用 EM 仿真、寄生建模和封装建模。

系统预算参数

RF IC 设计还根据关键参数的“系统预算”给出了性能要求和约束,例如噪声系数、功率、相位噪声、谐波、线性度等。该预算由系统级设计团队确定,它将预算限制和性能要求传递给负责系统图中每个模块的射频设计人员。这些模块进一步细分为拓扑和电路,并使用可处理 IC 的 EM 仿真工具进行设计、仿真、优化和布局仿真的迭代过程。

IC 设计限制

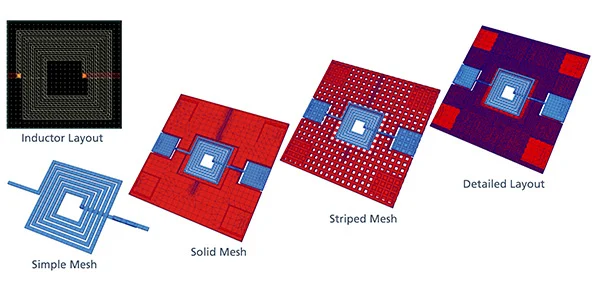

由于一些片上无源器件(例如电感器和电容器)受到代工厂的严重限制,射频 IC 设计人员通常对这些组件的尺寸和值的控制有限。这导致设计中存在更大的不确定性,并且可能需要与代工厂反复设计和测试新组件,以生产出能满足射频电路需求的组件。

在某些情况下,射频设计人员可能需要对键合线和其他与代工厂无关的封装动态进行额外建模,以准确预测终组装中的寄生效应和终器件性能。许多 RFIC 以裸芯片形式交付,并直接引线键合到组件或托盘中,而不是典型的 IC 封装和 PCB 放置。

电磁仿真

一旦 RF IC 进入物理布局阶段,通常会进行多次 EM 仿真、电路仿真和寄生参数提取,其中至少涉及 IC 封装,但也可能会考虑设备的 PCB 和外部电路。其原因是,射频电路与高度敏感的模拟电路非常相似,可能会因附近的外部电路、电场/磁场、温度、电磁信号和其他环境因素而经历巨大的性能变化。

即使在流片之后,在提交终设计和开始 RFIC 生产之前,通常也需要进行测试、模型增强和其他优化。

RF 抽象级别

以下是 RF IC 的一般抽象级别:

功能性

行为的

宏

电路

晶体管

物理布局

RFIC设计流程

以下描述了工程师设计射频集成电路时可能遵循的工作流程:

设计规范

规格

约束条件

拓扑结构

测试台开发

系统设计

高层系统设计和预算

行为建模

电路综合

HDL 混合级 SIM

混合级分区

电路设计

使用铸造设计套件

螺旋电感器综合/建模

详细电路设计

电路仿真

时域

频域

物理设计

布局

电磁模拟与提取

寄生提取

片上无源器件的提取

封装寄生效应的提取

设计规则检查(DRC)

布局与原理图 (LVS)

系统测试台验证

签收 网络提取/流片

版权与免责声明

凡本网注明“出处:维库电子市场网”的所有作品,版权均属于维库电子市场网,转载请必须注明维库电子市场网,https://www.dzsc.com,违反者本网将追究相关法律责任。

本网转载并注明自其它出处的作品,目的在于传递更多信息,并不代表本网赞同其观点或证实其内容的真实性,不承担此类作品侵权行为的直接责任及连带责任。其他媒体、网站或个人从本网转载时,必须保留本网注明的作品出处,并自负版权等法律责任。

如涉及作品内容、版权等问题,请在作品发表之日起一周内与本网联系,否则视为放弃相关权利。

- RF设计基础知识 - 传输线的引入2025/3/3 16:41:26

- AD9361和AD9371里接收机的性能有哪些不同呢2025/1/16 17:51:40

- 如何使用双线线圈来设计高频射频应用的变压器2024/11/15 16:21:43

- RFID是什么?RFID读写器的工作原理2024/11/13 17:19:57

- RF设计基础——传输线简介2024/8/13 16:44:09