如何利用简单的布局规则解决 PCB 开关噪声

出处:维库电子市场网 发布于:2024-07-01 16:51:35

当具有高阻抗终端的 PCB 走线与具有快速变化电压的走线(例如数字或时钟信号)相邻时,就会出现信号耦合问题。只需两条走线即可构建这种易于构建的 PCB 电容。这种噪声的原因是高速信号,例如电压随时间快速变化(V/t)的数字电平移位和高阻抗走线。

如何利用简单的布局规则解决 PCB 开关噪声

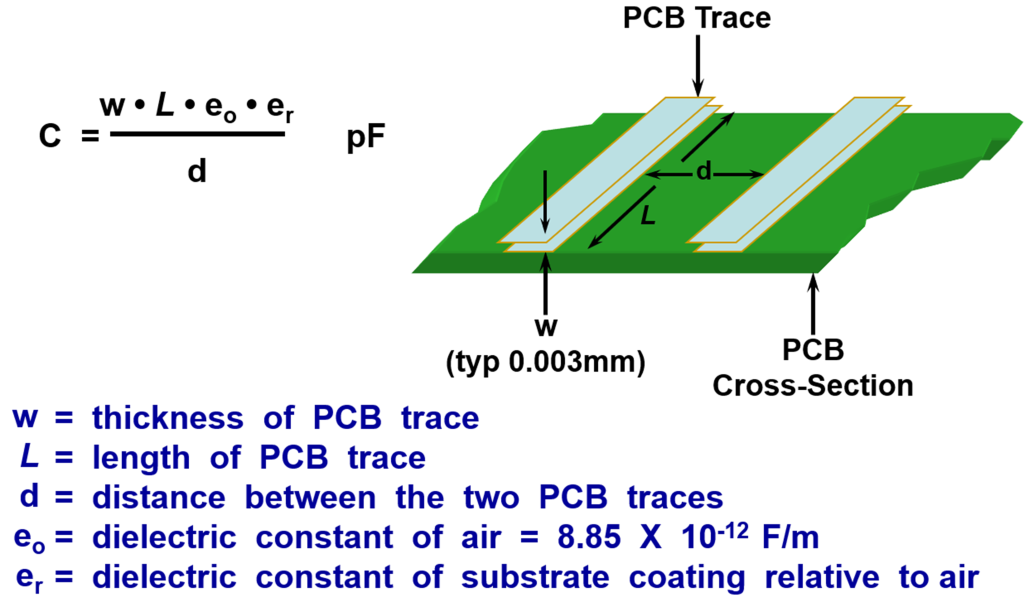

图 1使用 PCB 走线厚度 (w)、距离 (d) 和长度 (L) 尺寸来确定两条走线之间的电容。德州仪器

空气介电常数(e o)和介电常数e r ——取决于玻璃编织类型、厚度、树脂含量以及走线周围基材涂层的铜箔粗糙度——构成了新电容器的终公式。

此类 PCB 电容器的如下图所示,为例 1:

L = 1 英寸或 25.4 毫米d = 0.2 毫米

宽度 = 0.003 毫米

e o = 8.85 x 10 -12 F/m

e r = 4.8(FR4 PCB 材料)

外部走线电容噪声

当一条走线有数字时钟信号时,该信号会以电流而非电压的形式耦合到其他走线。关键的时钟特性是走线的数字信号具有快速的上升和下降时间。另一个条件是接收走线具有高阻抗端接,例如缓冲器配置中放大器的输入(图 2)。

图 2如果电压 CLK 轨迹上的上升和下降时间随时间快速变化,则信号在第二条轨迹上显示为电流尖峰。保护轨迹会破坏电场并减弱耦合现象。德州仪器

第二条迹线的电流尖峰的幅度取决于迹线间电容和第二条迹线的端接电阻幅度。

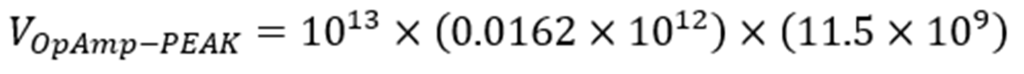

将示例 1 进一步推进至示例 2:

R IN = 10 13 W(运算放大器输入阻抗)

C = 0.0162 x 10 -12法拉(PCB 电容)

V/t = (3.3 x 0.8 V)/230 ps = 11.5 x 10 9 V/秒(100-MHz 时钟)

运算放大器输出端的峰值电压如下面的公式 2 所示:

如何让电路恢复正常

让我们将一些氧气带回这个系统。有两种策略可以尝试:增加走线之间的距离并添加接地保护走线。一个实用的解决方案是将走线彼此分开。由于走线之间的临界距离 (d) 在公式 1 的分母中,因此电容将相反地减小。

第二种策略是在两条原始走线之间放置一条额外的接地走线。如果在这两条走线之间放置一条保护走线,则会对电场造成干扰。通常,干扰足以衰减整个外部噪声效应。

在设计下一个 PCB 时,重新研究基础知识绝不会有什么坏处。本博客介绍了来自相邻 PCB 走线的无意外部噪声。拿出您的铅笔和纸,量化潜在的噪声源。

版权与免责声明

凡本网注明“出处:维库电子市场网”的所有作品,版权均属于维库电子市场网,转载请必须注明维库电子市场网,https://www.dzsc.com,违反者本网将追究相关法律责任。

本网转载并注明自其它出处的作品,目的在于传递更多信息,并不代表本网赞同其观点或证实其内容的真实性,不承担此类作品侵权行为的直接责任及连带责任。其他媒体、网站或个人从本网转载时,必须保留本网注明的作品出处,并自负版权等法律责任。

如涉及作品内容、版权等问题,请在作品发表之日起一周内与本网联系,否则视为放弃相关权利。

- PCB板层设计与电磁兼容性的关系解析2025/9/26 13:01:30

- 铜基板是什么?一文读懂“散热界的扛把子”2025/9/9 9:03:53

- 盲孔、埋孔、通孔、半孔——电路板孔洞的四大分类解析2025/9/9 8:59:38

- LDO 电源 PCB 设计从原理到布局要点2025/9/4 16:28:44

- 深度剖析 PCB 晶振设计:工作原理与详细步骤指南2025/9/3 11:02:26