通过创建 4 位二进制计数器在 VHDL 中实现有限状态机

出处:维库电子市场网 发布于:2024-09-02 16:03:09

在深入研究设计之前,让我们快速回顾一下有限状态机。它们是时序逻辑电路的抽象数学模型,在任意给定时刻,它们只在有限数量的状态之一中运行。

FSM 可以在每个时钟周期内在其状态之间转换。下一个状态基于外部输入和当前状态(这意味着它采用内存逻辑)。

有限状态机可用于检测或生成序列,并且是电梯、交通灯、自动售货机和电子锁等系统的基础。

二进制计数器

FSM 的一个特定实现是二进制计数器。这些电路的设计目标是迭代并显示所需的二进制数序列,通常使用一系列互连的触发器构建。二进制计数器的每个新状态都必须由输入脉冲触发,该脉冲可以来自外部源或来自电路自己的时钟信号。

有了这些背景知识,让我们深入研究 4 位二进制计数器的代码。

FSM 二进制计数器的 VHDL 代码

我们将通过在 VHDL 文件顶部声明几个库来开始编写二进制计数器的代码:

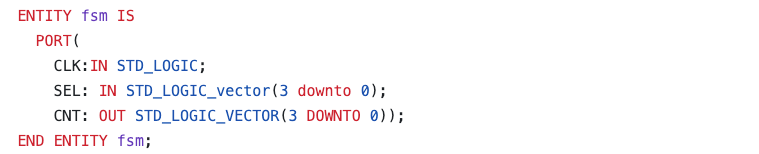

接下来,我们将为电路创建一个名为fsm的实体,并定义其输入和输出端口:

由命令“in std_logic”定义的时钟信号CLK输入一个名为CNT 的4 位输出端口,使用“out std_logic_vector(3 downto 0)”

一个名为SEL的 4 位输入端口,使用“in std_logic_vector(3 downto 0)”

流程和数据类型定义

现在我们已经定义了fsm实体,我们可以为我们的电路创建一个架构。该架构将有三个过程:

状态记忆。

下一个状态逻辑。

输出逻辑。

在我们创建这些过程之前,我们需要为我们的状态定义一种新的数据类型和两个该数据类型的信号变量来记住当前状态和下一个状态(将它们视为寄存器)。

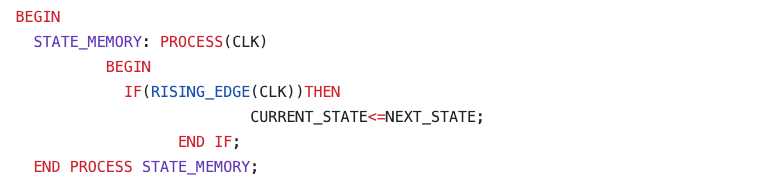

状态记忆过程

现在我们可以创建个名为STATE_MEMORY的进程。使用IF语句,它在CLK信号的每个上升沿将下一个状态的值写入当前状态变量中。

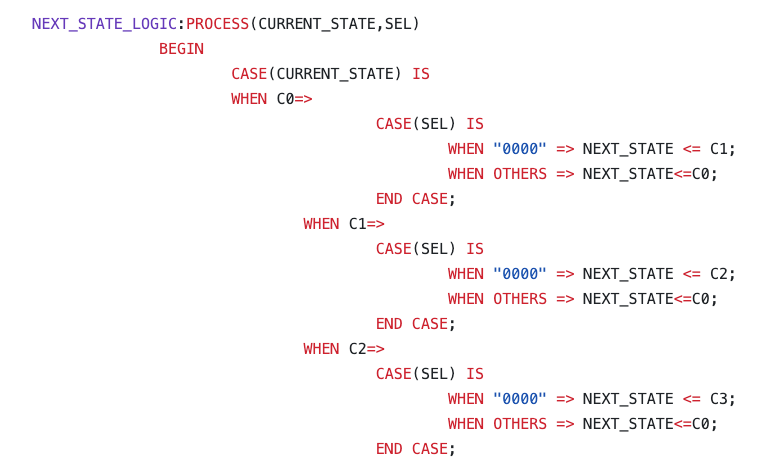

我们将使用SEL输入端口和CURRENT_STATE信号创建一个名为NEXT_STATE_LOGIC的进程。在这个进程中,我们为当前状态调用一个CASE-WHEN语句。我们在个CASE-WHEN语句的每个WHEN子句内嵌套了用于模式的其他CASE-WHEN语句。

这样,我们就有了一个架构,它首先检查FSM的当前状态,然后从SEL端口读取值。当此过程完成时,一个嵌套的WHEN子句将根据我们的代码将正确的下一个状态值写入NEXT_STATE信号(写入正在计数的序列)。

下面的代码块显示了一个简单的递增计数器,当SEL端口值等于“0000”时,该计数器处于活动状态。为简洁起见,我仅显示了其中几个重复的 case 语句,但完整的代码在下面提供。

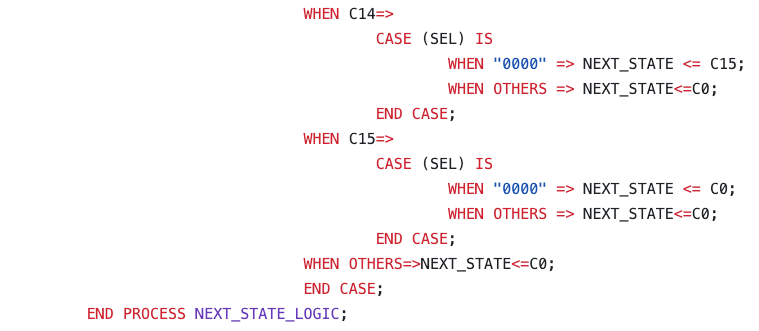

跳过类似的 C3 到 C13 的情况,我们到达NEXT_STATE_LOGIC过程的末尾,其中:

,为了将当前状态输出到 4 位 LED 显示屏上,我们需要编写另一个名为OUTPUT_LOGIC的过程。它用相应的 4 位二进制数枚举我们之前定义的每种状态类型。

这再次通过使用CURRENT_STATE信号并调用另一个CASE-WHEN语句来完成。CNT输出以其 4 位二进制对应项表示当前状态:

上一篇:几种toString的性能对比

版权与免责声明

凡本网注明“出处:维库电子市场网”的所有作品,版权均属于维库电子市场网,转载请必须注明维库电子市场网,https://www.dzsc.com,违反者本网将追究相关法律责任。

本网转载并注明自其它出处的作品,目的在于传递更多信息,并不代表本网赞同其观点或证实其内容的真实性,不承担此类作品侵权行为的直接责任及连带责任。其他媒体、网站或个人从本网转载时,必须保留本网注明的作品出处,并自负版权等法律责任。

如涉及作品内容、版权等问题,请在作品发表之日起一周内与本网联系,否则视为放弃相关权利。

- SQL核心知识点总结2025/8/11 16:51:36

- 等电位端子箱是什么_等电位端子箱的作用2025/8/1 11:36:41

- 基于PID控制和重复控制的复合控制策略2025/7/29 16:58:24

- 什么是树莓派?一文快速了解树莓派基础知识2025/6/18 16:30:52

- 什么是有机液分析与有机液知识介绍2025/6/7 16:31:44