LVDS:高速、低功耗、稳健的数据传输

出处:网络整理 发布于:2025-01-02 17:18:47

但当数字数据(尤其是高速数据)离开这个受保护的环境时(例如,当它必须通过长电缆或强烈的 EMI 传输到系统的单独部分时),情况就会发生变化。当存在强噪声源或需要非常高的数据速率(例如,每秒数百兆比特)时,甚至板内通信也可能成为问题。

从一根线到两根线

在这种情况下,一般的补救措施是从单端逻辑转向差分信号。RS-422/485是一个的接口,但它并未针对高速进行优化。其他选项包括电流模式逻辑 (CML) 和低压正发射极耦合逻辑 (LVPECL)。但是,根据我的经验,更常见的选择是低压差分信号 (LVDS)。

LVDS 是一种用于高速、点对点数字通信的标准化接口。 “点对点”是指一台发射器和一台接收器; LVDS 并不是为了促进系统中众多设备之间的通信,而是为了快速有效地将大量数据从一个设备移动到另一设备。

信号

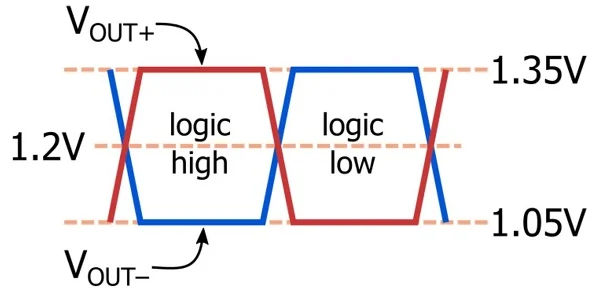

LVDS 使用(您猜对了!)低电压摆幅差分信号,如下所示:

尽管逻辑低电平和逻辑高电平之间的电压差很小,但差分信号(与双绞线和屏蔽电缆结合使用)的优点使 LVDS 能够提供高度可靠的通信。

低压优势

低压摆幅信令不仅仅是数据完整性问题,还可以节省电力并提高速度:

端接电阻器两端的电压越低,电流就越小,而电源电压越低,通常会降低功耗(请记住,CMOS 功耗与 VDD平方 成正比)。

电压转换不能立即发生;信号从一种电压转移到另一种电压需要时间,因此逻辑低电平和逻辑高电平之间的距离较短,可以通过减少每次逻辑转换所需的时间来实现更高频率的操作。

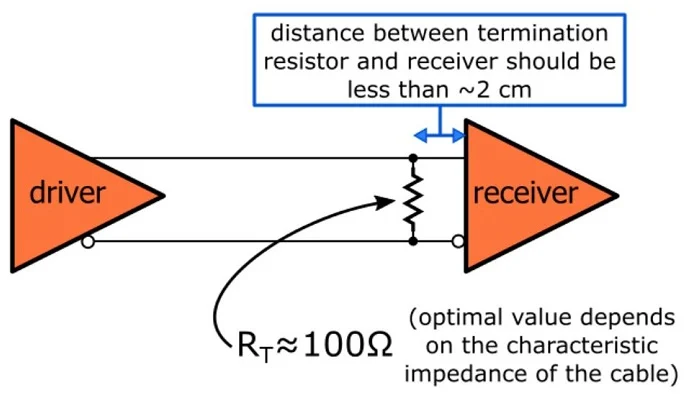

LVDS 是一种高性能标准,可以实现接近甚至超过每秒 1 GB 的数据速率(尽管速度必须随着电缆长度的增加而降低)。但不要被吓倒——大量用户友好的集成电路使 LVDS 成为一个非常平易近人的接口。使用现成的 LVDS 驱动器和接收器将标准逻辑转换为 LVDS,然后再转换回标准逻辑并不困难,而且终止也很简单:

版权与免责声明

凡本网注明“出处:维库电子市场网”的所有作品,版权均属于维库电子市场网,转载请必须注明维库电子市场网,https://www.dzsc.com,违反者本网将追究相关法律责任。

本网转载并注明自其它出处的作品,目的在于传递更多信息,并不代表本网赞同其观点或证实其内容的真实性,不承担此类作品侵权行为的直接责任及连带责任。其他媒体、网站或个人从本网转载时,必须保留本网注明的作品出处,并自负版权等法律责任。

如涉及作品内容、版权等问题,请在作品发表之日起一周内与本网联系,否则视为放弃相关权利。

- CAN XL 通信技术在车载毫米波雷达中的应用 (2)2025/8/8 16:24:00

- 光纤线和网线有啥区别2025/8/7 17:21:57

- 网线怎么排2025/8/1 11:42:44

- 全面对比:光纤线与网线的差异大揭秘2025/7/30 17:00:38

- SPI 通信协议的基本概念和工作模式2025/7/30 16:53:59