电路板 ESD 保护优化:实用小窍门大揭秘

出处:网络整理 发布于:2025-07-11 16:19:22

设备安置和布局

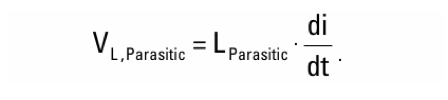

要使 ESD 保护器发挥功效,器件的位置和布局起着至关重要的作用。设计人员需要深入了解各种寄生电感对电路板的影响,其中电感是需要特别关注的因素。因为仅通过 1nH 的 8kV ESD 冲击(即 30A),就会在 PCB 线路上产生 30V 的尖峰电压。

注:本讨论假定所有 ESD 威胁都通过图 1 中的端口进入系统。

LESD 和 LGND

有时,由于电路板布局的限制,无法将 ESD 器件直接放置在 PCB 线路上。原因多种多样,但无论如何,将静电放电元件放置在距离受保护数据线一厘米远的地方,就可能迅速转化为数十伏的电压。GND 总线也存在类似情况,在某些设计中,ESD 器件的 GND 必须通过多个通孔,甚至要经过迂回路径才能到达 GND 平面。除了流经 ESD 设备的 ESD 电流所产生的电压外,这两个电感还会产生电压尖峰(即 IPEAK * RDYNAMIC)。下面通过一个简化示例来说明 LESD 和 LGND 对 VIC 的影响。在举例之前,需要说明的是,常见的 PCB 制造工艺可为典型的微带线迹提供约 3nH/cm(假设具有一定的宽度、厚度和介电常数)。有鉴于此,我们假设一个 8kV 的 ESD 脉冲和一个动态电阻为 1Ω 的 ESD 器件。同时,考虑两种不同的布局,布局 A 和布局 B,它们的 LESD = LGND = 1.5nH(各为 0.5cm)和 LESD = LGND = 3.0nH(各为 1.0cm)。由此可见,只要将痕量长度(即 LESD 和 LGND)从 0.5cm 增加到 1cm,VIC 就能增加 75%。图 2 显示了布局 B 以及与每个元件相关的电压。

LIC 和 LPORT

利用 LIC 和 LPORT 是提高整体 ESD 性能的直接方法。不过,有些设计无论上述比率多低,都会过早失效。也就是说,LIC 的值无法为峰值 ESD 电流提供足够的缓冲。

缓冲电阻

通过增加一个 10Ω 的缓冲电阻,流入集成电路的峰值电流可降低近 50%(在本例中)。显然,电阻值可以增加到 10Ω 以上,以进一步减小泄放电流,而电阻值往往取决于应用的具体情况。还应注意的是,在 HDMI 和 USB 3.0 等一些高速应用中使用这种技术时必须格外小心。RBUFFER 电阻会干扰线路阻抗,使信号衰减超出这两种标准的合规规格,但精心的电路板设计可以弥补任何不良影响。不过,电路板设计人员应在工具箱中保留这项技术,并在电路板或系统内 ESD 电平低于要求时加以应用。

结束语

下一篇:消弧线圈的工作原理

版权与免责声明

凡本网注明“出处:维库电子市场网”的所有作品,版权均属于维库电子市场网,转载请必须注明维库电子市场网,https://www.dzsc.com,违反者本网将追究相关法律责任。

本网转载并注明自其它出处的作品,目的在于传递更多信息,并不代表本网赞同其观点或证实其内容的真实性,不承担此类作品侵权行为的直接责任及连带责任。其他媒体、网站或个人从本网转载时,必须保留本网注明的作品出处,并自负版权等法律责任。

如涉及作品内容、版权等问题,请在作品发表之日起一周内与本网联系,否则视为放弃相关权利。

- 全面解析断路器越级跳闸:原因、处理与要点总结2025/7/30 16:25:03

- IGBT 元件短路与过电压保护的关键要点解析2025/7/24 15:49:28

- 消弧线圈的工作原理2025/7/18 16:57:11

- 线性稳压器 IC 的过电流保护与过热保护2025/7/8 15:57:38

- 什么是浪涌保护器,浪涌保护器的知识介绍2025/7/7 17:29:37