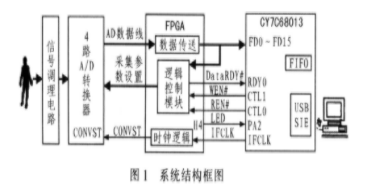

1 引言 生物电信号是由生物体发出的不稳定的微弱电信号,主要包括心电、肌电、脑电信号,其特点表现为信号弱、干扰强、 高。因此,在生物体的多参数测量中,高 尤...

时间:2020-08-14 阅读:613 关键词:基于接口芯片与FPGA器件实现生物电信号数据采集的设计芯片,FPGA器件

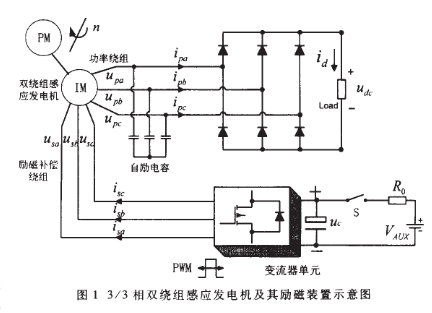

介绍了针对3/3相双绕组感应发电机设计的励磁系统,该系统由DSP和FPGA构成。给出了控制系统的接口电路和实验结果。 1 、系统简介 3/3相双绕组感应发电机带有两个绕组...

分类:工业电子 时间:2020-04-14 阅读:794 关键词:采用DSP和FPGA器件实现电机励磁控制系统的设计DSP,电机

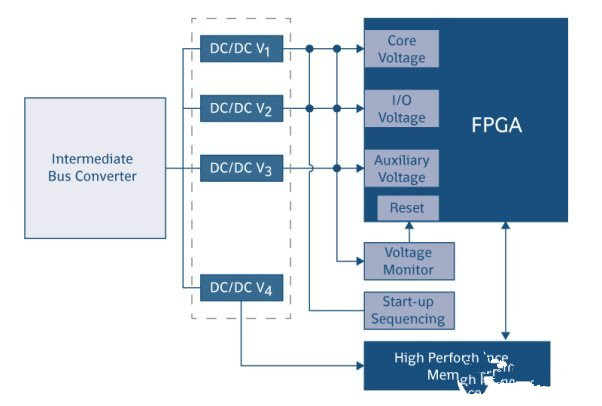

描述电源系统的需求很容易,执行这些需求却更具挑战性。只要它比上一代产品更小、更可靠、更有效且成本更低,那么设计经理、营销团队和用户就会很高兴。FPGA等现代半导体器...

分类:电源技术 时间:2020-03-04 阅读:656 关键词:FPGA器件,电源模块

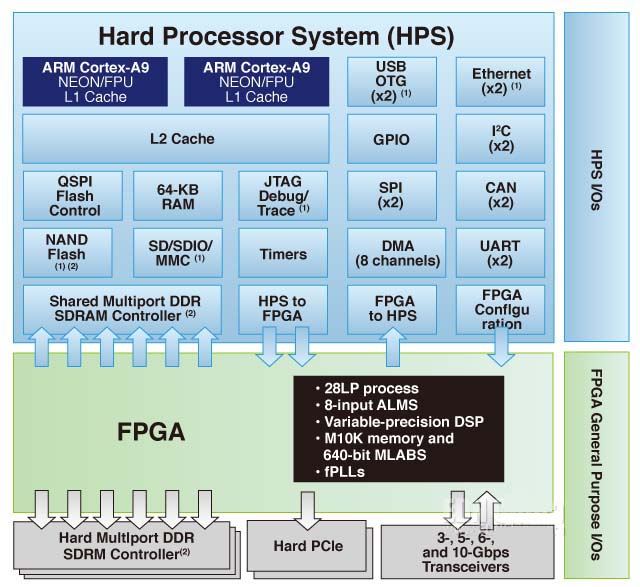

随着物联网应用程序的采用势头越来越大,嵌入式开发社区面临的压力也越来越大,以便兼顾每种设计的可用计算资源,延迟,成本和大小。由于其实时性,对云连接的关注也被视为一些发展的挑战,导致混合“雾”计算方法。...

引言 数据采集设备是测试系统中不可缺少的一部分,数据采集需要针对不同类型的需求,需要有高速A/D、低速A/D、数字多用表等功能,传统数据采集设备是用一种仪器进行一类测试,通过多种仪器组合实现一组完整测试,这...

分类:单片机与DSP 时间:2019-01-11 阅读:162 关键词:基于DSP技与+FPGA器件实现数据采集设备的小型化DSP,FPGA器件

主要FPGA供应商已经开始销售集成了硬核处理器内核的低成本FPGA器件,SoC类FPGA器件最终会成为主流。为能够充分发挥所有重要FPGA的灵活性,这些器件提供了FPGA设计人员和软...

分类:EDA/PLD/PLC 时间:2012-11-07 阅读:2445 关键词:SoC类FPGA器件设计难题解决方案SoCFPGACortex-A9

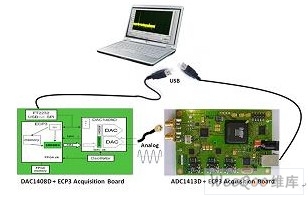

NXP新款CGV高速转换器演示板采用LatticeECP3 FPGA器件

恩智浦半导体(NXP Semiconductors)近日宣布,CGV高速数据转换器系列新增两款低成本、低功耗演示板,新产品采用了莱迪思半导体公司生产的LatticeECP3器件。新演示板旨在证明...

分类:EDA/PLD/PLC 时间:2010-06-01 阅读:4137 关键词:NXP新款CGV高速转换器演示板采用LatticeECP3 FPGA器件FPGA器件转换器

Actel推出智能型混合信号FPGA器件SmartFusion

爱特公司(Actel Corporation)宣布推出世界智能型混合信号FPGA器件SmartFusion,该产品现正投入批量生产。SmartFusion器件带有Actel经过验证的FPGA架构,该架构包括基于ARM ...

分类:EDA/PLD/PLC 时间:2010-03-09 阅读:3415 关键词:Actel推出智能型混合信号FPGA器件SmartFusionFPGA器件

爱特公司(ActelCorporation)宣布推出世界首个智能型混合信号FPGA器件SmartFusion,该产品现正投入批量生产。SmartFusion器件带有Actel经过验证的FPGA架构,该架构包括基于ARMCortex-M3硬核处理器的

分类:EDA/PLD/PLC 时间:2010-03-05 阅读:3549 关键词:Actel推出世界首个智能型混合信号FPGA器件FPGA

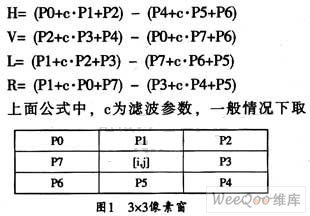

0引言 边缘检测技术是图像处理的一项基本技术,在工业、航天、医学、军事等领域中有着广泛的应用。边缘检测算法的实现涉及复杂的计算步骤,故对处理速度有较高要求。采...

分类:EDA/PLD/PLC 时间:2009-10-30 阅读:2598 关键词:基于FPGA器件的Sobel算法实现FPGA器件

CPLD和FPGA都支持边界扫描(JTAG)模式,JTAG端口用于边界扫描测试、器件配置、应用诊断等,符合IEEE 1532/IEEE 1149,1规范。每个CPLD/FPGA器件都有专用的JTAG端口,JTAG端口有4个引脚,具体描述见表1。 通过JTA...

分类:EDA/PLD/PLC 时间:2008-12-08 阅读:3791 关键词:CPLD/FPGA器件的配置方法1149CPLDFPGA

实现PLD器件功能最关键的技术是计算机辅助设计(CAD)。CAD技术和设计软件及开发环境对于 CPLD/FPGA的设计至关重要,尤其是FPGA器件更依赖于开发软件,CPLD/FPGA器件厂商都推出了自己的集成 开发环境(IDE),Xilinx...

分类:EDA/PLD/PLC 时间:2008-12-08 阅读:2576 关键词:CPLD/FPGA器件的开发过程CPLDFPGA

低功耗、可重编程的RT ProASIC3器件简化了航天系统的设计 为了继续提供满足航天设计人员需求的创新硅解决方案,Actel宣布推出业界面向太空飞行应用以Flash为基础,耐辐射的FPGA器件。全新的低功耗RT ProASIC?3器...

在设计XilinxFPGA器件去耦网络时,首先需要用ISE1O的设计工具规划器件的每个输入/输出块(Bank)的SSO(SimultaneouslySwitchingOutput,同步转换输出)个数,因为SSO是造成地线反弹和交调干扰的根源,每个B

分类:EDA/PLD/PLC 时间:2008-09-16 阅读:2529 关键词:Xilinx FPGA器件的去耦网络设计范例FPGA器件去耦网络

在配置FPGA器件时的常见问题及其解决方法。 (1)当模式改变后,同时需要修改产生位流文件中的配置时钟的属性为CCLK或JTAGClock,否则无法配置。 (2)DONE状态脚始终为低解决方法:检查该引脚的负载是否太重,选...

分类:EDA/PLD/PLC 时间:2008-09-16 阅读:2793 关键词:配置FPGA器件时的常见问题FPGA器件

Xilinx的FPGA器件配置流程共有4个阶段,每个阶段分别执行不同的命令和操作。这4个阶段分别为配置存储器清除、初始化、装入配置数据和启动器件,下面以Spartan-3的加载为例说明这个过程。 (1)配置存储器清除阶段(...

分类:EDA/PLD/PLC 时间:2008-09-16 阅读:2065 关键词:FPGA器件配置流程FPGA器件

只有成功配置可编程逻辑器件FPGA之后,器件才能正常工作。Xilinx FPGA的配置有3种模式,分别为并行(SelectMap)、串行(Serial)和边界扫描(Boundary Scan)模式。当然Virtex-5和Spartan-3E/3A的器件有更多的配置模式,...

分类:EDA/PLD/PLC 时间:2008-09-16 阅读:3357 关键词:FPGA器件配置模式XC17FPGA器件