CA3240, CA3240A

Electrical Specifications

For Equipment Design, at V+ = 5V, V- = 0V, T

A

= 25

o

C, Unless Otherwise Specified

(Continued)

TYPICAL VALUES

PARAMETER

Common-Mode Rejection Ratio

SYMBOL

CMRR

CA3240A

32

90

Common-Mode Input Voltage Range (See Figure 24)

V

ICR

PSRR

-0.5

2.6

Power Supply Rejection Ratio

31.6

90

Maximum Output Voltage (See Figures 23, 24)

V

OM

+

V

OM

-

Maximum Output Current

Source

Sink

Slew Rate (See Figure14)

Gain Bandwidth Product (See Figure 13)

Supply Current (See Figure 15)

Device Dissipation

I

OM

+

I

OM

-

SR

f

T

I+

P

D

3

0.3

20

1

7

4.5

4

20

CA3240

32

90

-0.5

2.6

31.6

90

3

0.3

20

1

7

4.5

4

20

UNITS

碌V/V

dB

V

V

碌V/V

dB

V

V

mA

mA

V/碌s

MHz

mA

mW

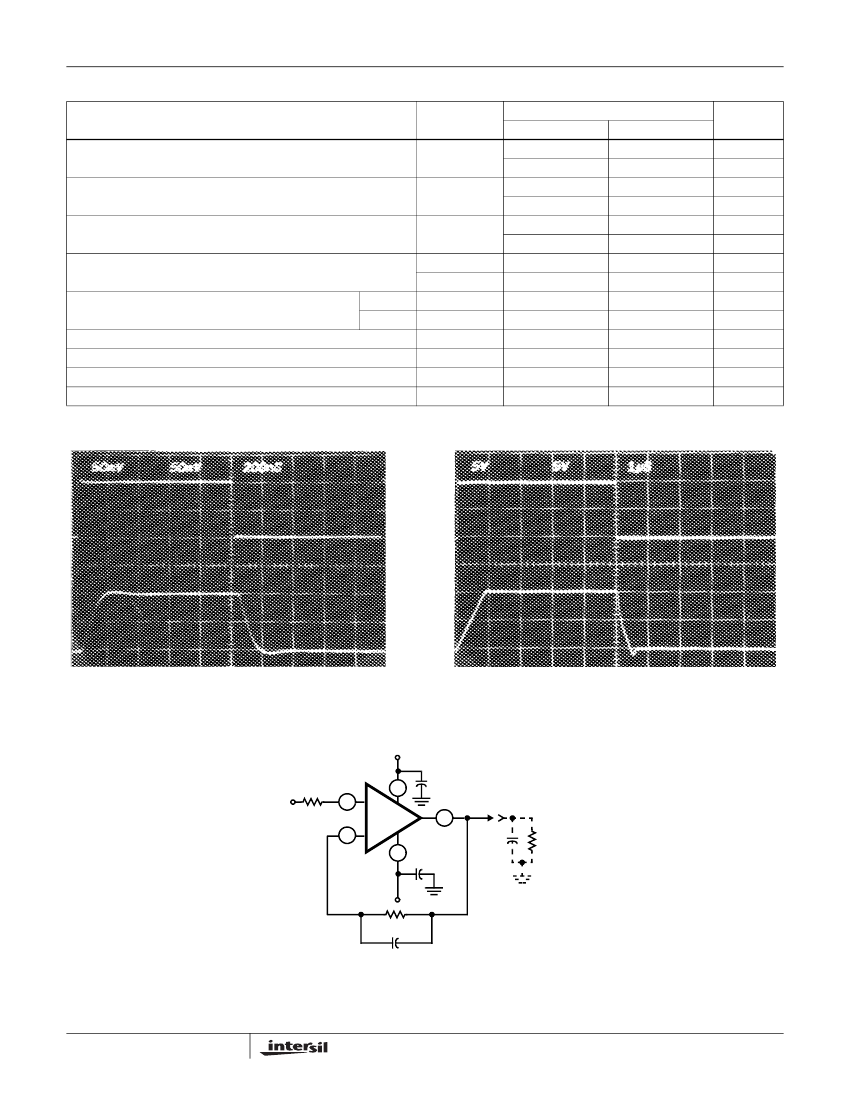

Test Circuits and Waveforms

50mV/Div., 200ns/Div.

Top Trace: Input, Bottom Trace: Output

FIGURE 1A. SMALL SIGNAL RESPONSE

+15V

10k鈩?/div>

+

CA3240

0.1碌F

5V/Div., 1碌s/Div.

Top Trace: Input, Bottom Trace: Output

FIGURE 1B. LARGE SIGNAL RESPONSE

SIMULATED

LOAD

2k鈩?/div>

-

0.1碌F

100pF

-15V

2k鈩?/div>

0.05碌F

BW (-3dB) = 4.5MHz

SR = 9V/碌s

FIGURE 1C. TEST CIRCUIT

FIGURE 1. SPLIT-SUPPLY VOLTAGE FOLLOWER TEST CIRCUIT AND ASSOCIATED WAVEFORMS

4

FN1050.6

March 4, 2005