CY7C4421/4201/4211/4221

CY7C4231/4241/4251

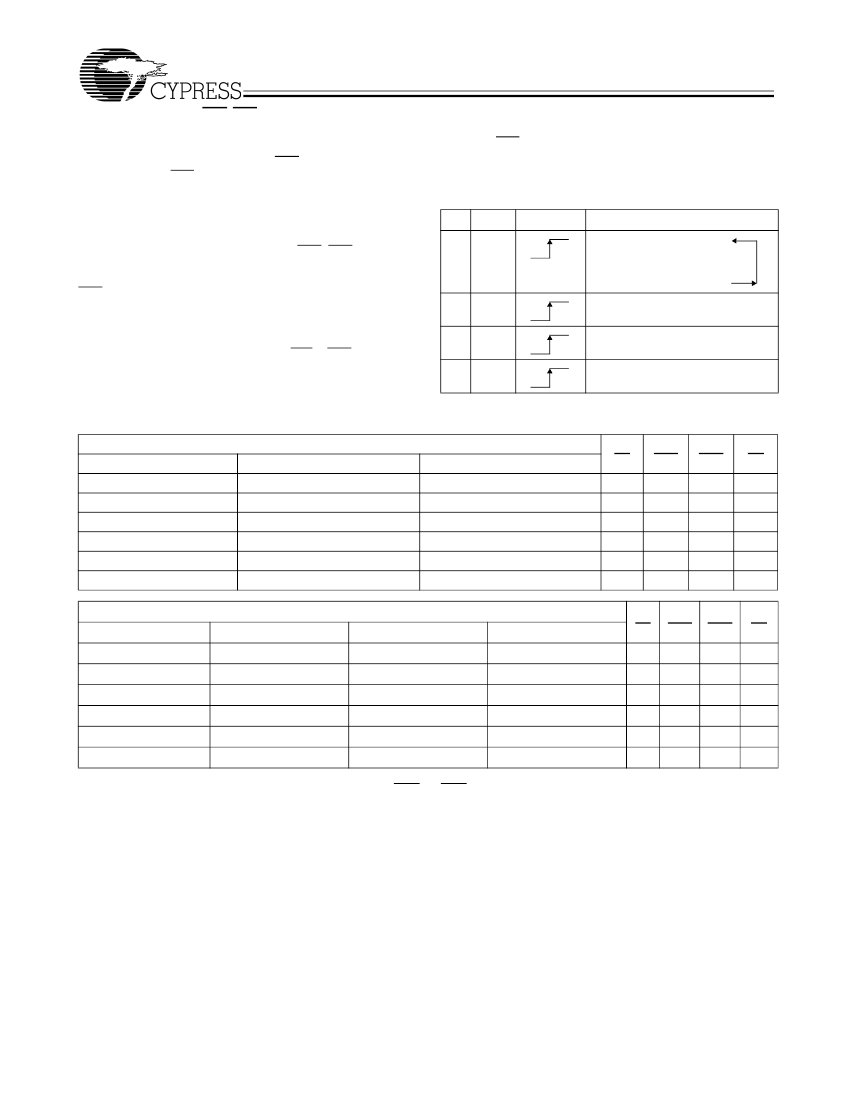

Programmable Flag (PAE, PAF) Operation

Whether the flag offset registers are programmed as

described in

Table 1

or the default values are used, the

programmable almost-empty flag (PAE) and programmable

almost-full flag (PAF) states are determined by their corre-

sponding offset registers and the difference between the Read

and Write pointers.

The number formed by the empty offset least significant bit

register and empty offset most significant register is referred

to as

n

and determines the operation of PAE. PAE is synchro-

nized to the LOW-to-HIGH transition of RCLK by one flip-flop

and is LOW when the FIFO contains n or fewer unread words.

PAE is set HIGH by the LOW-to-HIGH transition of RCLK when

the FIFO contains (n + 1) or greater unread words.

The number formed by the full offset least significant bit

register and full offset most significant bit register is referred to

as

m

and determines the operation of PAF. PAE is synchro-

nized to the LOW-to-HIGH transition of WCLK by one flip-flop

and is set LOW when the number of unread words in the FIFO

is greater than or equal to CY7C4421. (64 鈥?m), CY7C4201

Table 2. Status Flags

Number of Words in FIFO

CY7C4421

0

1 to n

[2]

(n + 1) to 32

33 to (64 鈥?(m + 1))

(64 鈥?m)

64

[3]

(256 鈥?m), CY7C4211 (512 鈥?m), CY7C4221 (1K 鈥?m),

CY7C4231 (2K 鈥?m), CY7C4241 (4K 鈥?m), and CY7C4251

(8K 鈥?m). PAF is set HIGH by the LOW-to-HIGH transition of

WCLK when the number of available memory locations is

greater than m.

Table 1. Writing the Offset Registers

LD

0

WEN

0

WCLK

[1]

Selection

Empty Offset (LSB)

Empty Offset (MSB)

Full Offset (LSB)

Full Offset (MSB)

No Operation

Write Into FIFO

No Operation

0

1

1

1

0

1

CY7C4201

0

1 to n

[2]

(n + 1) to 128

129 to (256 鈥?(m + 1))

(256 鈥?m)

256

[3]

CY7C4211

0

1 to n

[2]

(n + 1) to 256

257 to (512 鈥?(m + 1))

(512 鈥?m)

512

[3]

FF

H

H

H

H

H

L

PAF

H

H

H

H

L

L

PAE

L

L

H

H

H

H

EF

L

H

H

H

H

H

to 63

to 255

to 511

Number of Words in FIFO

CY7C4221

0

1 to n

[2]

(n + 1) to 512

(1024 鈥?m)

[3]

to 1023

1024

0

1 to n

[2]

(n + 1) to 1024

(2048 鈥?m)

[3]

to 2047

2048

CY7C4231

0

1 to n

[2]

(n + 1) to 2048

(4096 鈥?m)

[3]

to 4095

4096

CY7C4241

0

1 to n

[2]

(n + 1) to 4096

(8192 鈥?m)

[3]

to 8191

8192

CY7C4251

FF

H

H

H

H

H

L

PAF

H

H

H

H

L

L

PAE

L

L

H

H

H

H

EF

L

H

H

H

H

H

513 to (1024 鈥?(m + 1)) 1025 to (2048 鈥?(m + 1)) 2049 to (4096 鈥?(m + 1)) 4097 to (8192 鈥?(m + 1))

Notes:

1. The same selection sequence applies to reading from the registers. REN1 and REN2 are enabled and a Read is performed on the LOW-to-HIGH transition of

RCLK.

2. n = Empty Offset (n = 7 default value).

3. m = Full Offset (m = 7 default value).

Document #: 38-06016 Rev. *A

Page 4 of 18