EPROM Memory Programming Specification

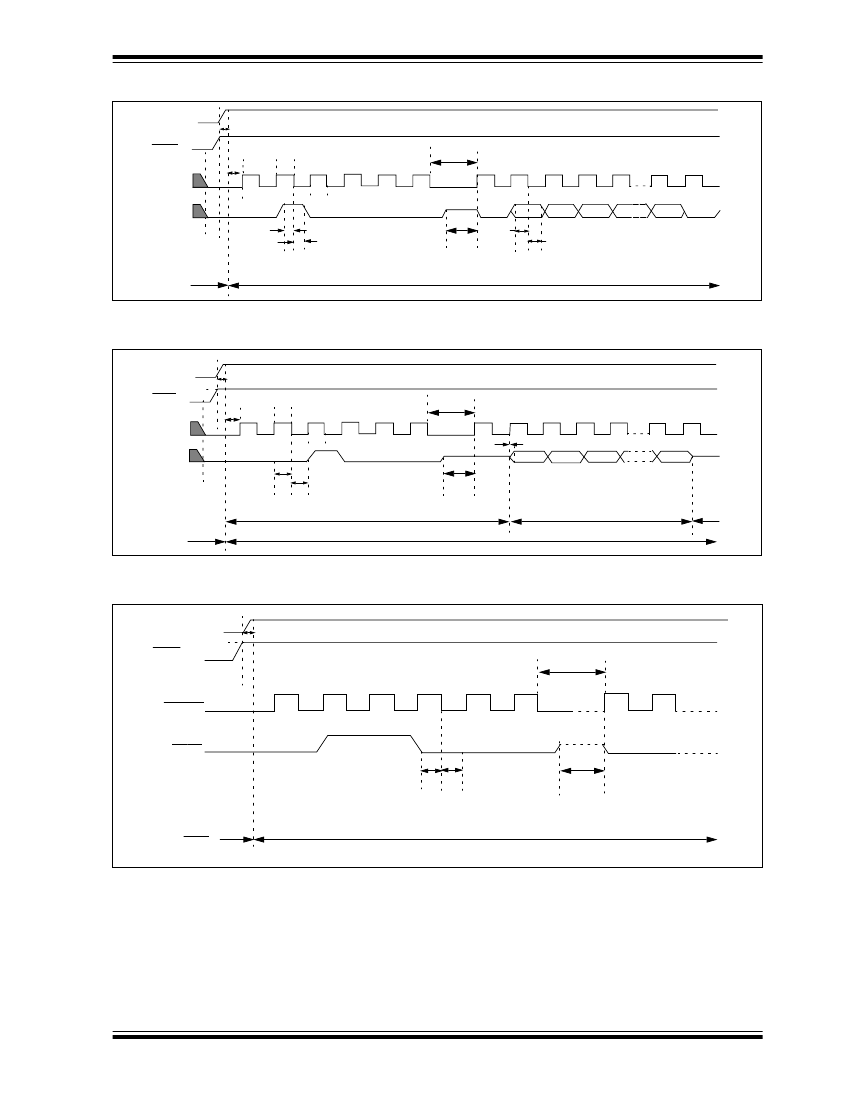

FIGURE 4-1:

V

IHH

MCLR/V

PP

P8 1

GP1

(CLOCK)

GP0

(DATA)

0

P3

P4

100n

s

min.

Reset

1

100ns

0

0

0

0

P5

1碌s min.

P3

P4

100ns

2

3

4

5

6

P6

1碌s min.

1

2

3

4

5

15

LOAD DATA COMMAND (PROGRAM/VERIFY)

V

DD

P9

0

0

}

}

}

}

Program/Verify Mode

100n

s

min.

FIGURE 4-2:

V

DD

READ DATA COMMAND (PROGRAM/VERIFY)

P9

V

IHH

MCLR/V

PP

P8

GP1

(CLOCK)

GP0

(DATA)

0

P3

0

P4

100ns

1

0

0

0

P5

1碌s min.

RB7

input

1

100ns

2

3

4

5

6

P6

1碌s min.

1

2

3

4

5

15

P7

}

}

100n

s

min.

RB7 = output

Reset

Program/Verify Mode

FIGURE 4-3:

INCREMENT ADDRESS COMMAND (PROGRAM/VERIFY)

V

DD

P9

V

IHH

MCLR/V

PP

P6

1碌s min.

Next Command

1

2

1

GP1

(CLOCK)

GP0

(DATA)

2

3

4

5

6

0

1

1

0

0

0

P5

0

0

P3 P4

1碌s min.

Program/Verify Mode

Reset

}

}

100ns

min

漏

1998 Microchip Technology Inc.

DS40175A-page 12