基于FPGA的数字幅频均衡功率放大器的解决方案

出处:cncsterry 发布于:2010-11-08 17:24:49

摘要:提出了一种基于FPGA 的数字幅频均衡功率放大器的设计方案。系统在完成基于AD620前级小信号放大电路设计的基础上,分析了阻带网络的幅频特性;结合分析结果与FIR 滤波算法给出了相应的滤波器组成方案。后级功率放大电路采用分立MOS 管实现。

在现代通信系统中,码间干扰是制约通信质量的重要因素。为了减小码间干扰,需要对信道进行适当的补偿,以减小误码率,提高通信质量,接收机中能够补偿或减小接收信号码间干扰的补偿器称为均衡器。。本文提出了一种基于FPGA 的数字幅频均衡功率放大器的解决方案。

1 系统总体设计

本文设计了一种数字信号幅频均衡功率放大器的实现方案。设计主要由四个模块组成。分别为小信号放大,带阻网络衰减,数字信号幅度的均衡处理以及功率放大。其中小信号放大部分由精密度高、噪音系数小的运算放大器AD620 实现;数字信号处理部分以FPGA 为处理,辅助以A/D、D/A 模块进行模拟信号和数字信号的转换;末级功放电路采用分立的MOS管来实现。

2 硬件电路设计

2.1 前置放大电路设计

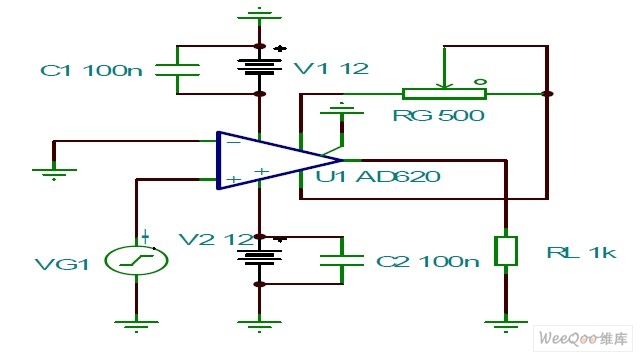

前置小信号放大器利用低功耗高的仪表运放AD620[3],在运放1 管脚和8 管脚之间介入可变电阻来实现增益可控,以满足题目中要求放大倍数不小于400 倍。前级放大电路如图1所示。根据AD620 的内部结构,其增益表达式如下:

Au=(R1+R2)/RG+1=49.4k Ω / RG+1,其中,RG 的单位为k Ω 。

图1 AD620 放大电路

2.2 带阻网络的计算

阻带网络电路(详见赛题)。根据基尔霍夫定律:

I1=I2+I3 (1)

U1= I1Z1+I3Z3 (2)

I3Z3= I2Z2+ U2 (3)

U2= I2RL=600*I2 (4)

由式(1)(2)(3)(4)得U1 、U2 的关系:

(其中,Z1、 Z2 、Z3 分别为各谐振网络的总阻抗)

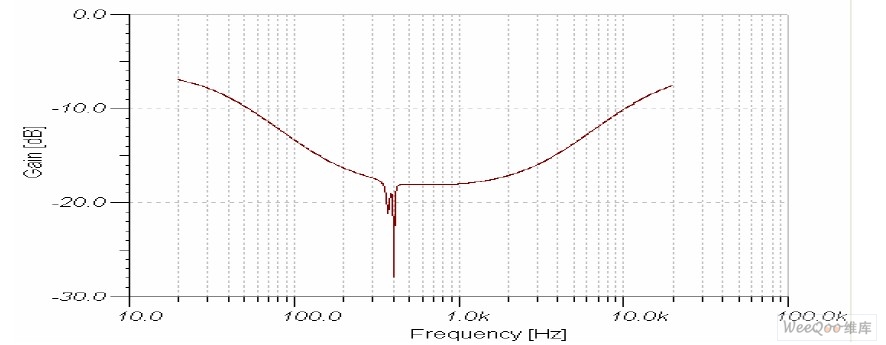

采用Tina 仿真软件中的Signal Analyzer 测得带阻网络输出信号的幅频特性如图2 所示。

图2 带阻网络输出信号的幅频特性

2.3 数字信号均衡处理模块电路设计

均衡技术的实质是在某种优化规则下完成随机信号的滤波。因此信号的幅频均衡问题即转变为滤波器的设计问题。在大多数使用均衡器的通信系统中,信道特性是未知的;并且在许多情况下,信道响应是时变的,在这种情况下,应将均衡器设计成对信道响应是可调的;对时变信道,应设计成对信道响应的时变是自适应的。所以自适应均衡器在通信系统中得到普遍应用。但本赛题中,因为其采用带阻网络模拟实际的信道,但带阻网络中所有器件参数均为固定值,不存在时变问题,故设计的滤波器系数无需自适应。

均衡模块采用Altera 公司的CycloneII 系列FPGA 作为信号滤波处理的; A/D 转换模块采用TI 的高速8 位A/D 转换器TLC5540,它的转换速率可达每秒40 兆字节;D/A 模块采用10 位高速转换芯片THS5651。

为实现对如图2 所示的衰减进行补偿,均衡模块采用了截止频率均为400HZ 的低通滤波器和高通滤波器的叠加。滤波器组原理图如图3 所示。

2.4 功率放大电路设计

根据题目要求,末级功率放大电路采用分立的大功率MOS 管实现,与分立的OCL 低功放相比,MOS 管功放具有激励功率小,输出功率大,输出漏极电流具有负温度系数,安全可靠,且有工作频率高,偏置简单等优点。电路如图3所示,以运放的输出作为OCL 的输入,达到抑制零点漂移的效果。此方案中用三极管来驱动MOS 管,集基极间的电容C4、C5 为高频防振电容。(注:图中数据为参考数值)

图3 MOS 管功率放大器

实际功率低于这个值,通过测量来计算出电路的效率。

3 软件设计

Altera 提供了基于Matlab、DSP Builder 的数字滤波器设计方法。使用DSP Builder可以方便地在图形化环境中设计FIR 滤波器,而且滤波器系数可以通过Matlab 的滤波器设计工具FDATool 计算完成。本文中采用直接I 型来实现该FIR 滤波器。首先设计一个系数可变的4 阶FIR 滤波器节。然后再通过不断的调用FIR 滤波器节,级联起来,从而完成高阶滤波器设计。

4 实验结果与结论

图4 singaltap 测试结果

图 4 为采用嵌入式逻辑分析仪SingalTap 得到的测试结果。其中,XIN 为由A/D 采样得到的输入信号,YOUT 为经过均衡程序处理过的输出信号。从输出YOUT 可明显观测到程序对输入信号作出了补偿,去除了噪声,稳定了波形,起到了均衡信号的作用。本设计充分利用 FPGA 在数字信号处理上的优势,在数字幅度均衡模块中以FPGA 为平台,实现数字信号幅度均衡的高速处理。同时本设计中前级放大电路不仅可以满足赛题中的各项指标,还可以实现增益的可选择性,可以在其他小信号放大的场合中运用。

参考文献:

[1]. AD620 datasheet https://www.dzsc.com/datasheet/AD620_122143.html.

[2]. TLC5540 datasheet https://www.dzsc.com/datasheet/TLC5540_1073968.html.

[3]. THS5651 datasheet https://www.dzsc.com/datasheet/THS5651_1074014.html.

版权与免责声明

凡本网注明“出处:维库电子市场网”的所有作品,版权均属于维库电子市场网,转载请必须注明维库电子市场网,https://www.dzsc.com,违反者本网将追究相关法律责任。

本网转载并注明自其它出处的作品,目的在于传递更多信息,并不代表本网赞同其观点或证实其内容的真实性,不承担此类作品侵权行为的直接责任及连带责任。其他媒体、网站或个人从本网转载时,必须保留本网注明的作品出处,并自负版权等法律责任。

如涉及作品内容、版权等问题,请在作品发表之日起一周内与本网联系,否则视为放弃相关权利。

- PLC的34个基础知识2024/1/17 16:25:58

- 印刷电路板的组装方法2023/9/15 17:04:46

- 模拟量输入测量值显示满量程(上溢)的故障处理方法2023/8/31 11:09:13

- 什么是PLC?看完就明白2023/5/5 16:37:01

- 可编程逻辑控制器 (PLC) 中的梯形逻辑2023/4/23 15:48:34