基于FPGA的数字视频接口转换器设计(二)

出处:电子爱好者博客 发布于:2013-05-16 10:21:24

3 系统硬件设计

系统的硬件设计主要包括:DVI接口的扩展显示数据 (EDID)设计,DVI接口接收电路、Camera Link接口发送电路及FPGA配置电路等FPGA外围电路设计及大容量存储器电路设计。

3.1 DVI接口EDI#D设计

DVI标准内含视频电子标准协会(VESA)制定的EDID标准及DDC2B协议。DDC2B协议构建于I2 C总线技术,用来读取接收设备所能支持的显示格式等EDID数据。只有接收设备符合DDC2B协议,且接收设备存储有正确的EDID数据时,计算机显卡才 会向接收设备输出TMDS视频信号。

系统选用基于DDC2B协议的AT24C02B来存储EDID数据,AT24C02B为256字节EEPROM,可存储EDID 1.2版本或更高版本的EDID数据。EDID结构包括视频分辨率、行场同步信号的时序特征、图像颜色深度、视频宽高比、版本号及设备制造商ID 等多种数据信息。EDTD 数据信息共占128个字节,被正确配置后,使用EEPROM 烧写器将有效数据存储在AT24C02B的前半部分地址空间,便完成了DVI接口的EDID设计。

3.2 FPGA外围电路设计

FPGA外围电路包括DVI接口接收电路,FPGA 配置电路,Camera Link接口发送电路。DVI接收芯片选用TI公司的TFP401A,Camera Link发送芯片选用国家半导体公司的DS90CR285,均为专用视频编解码芯片,接口电路遵循其参考设计进行开发即可,不再赘述。

FPGA为基于SRAM 架构的可编程逻辑器件,其内部功能逻辑在系统掉电时会丢失,因此,其外围配置电路是FPGA正常工作的保证。系统使用外部串行配置芯片(EPCS16)存 储FPGA配置数据,以实现系统上电时的FPGA程序自动加载。FPGA 配置模式设计为主动串行(Active Serial)加JTAG方式,配置电路如图2所示。由图可知,该电路设计简单,通过JTAG接口将sof文件加载到FPGA中,可实现程序的在线调试。 程序调试成功后,通过同一个JTAG接口,可将终的jic编程文件固化到EPCS16中。

3.3 存储器电路设计系统存储器电路由3片SRAM 芯片组成,可实现输入视频信号的帧缓存功能。系统输入的视频信号为XGA (1024×768@60Hz)格式,一帧图像的有效像素个数为1024×768个,而每个数字像素信号为24bits,故一帧视频信号的有效数据总量为 1024×768×24=18Mb.目前市场上,尚无任何一款SRAM、双口RAM 或FIFO芯片能单片满足存储XGA信号一帧图像数据的要求。系统使用三片1M×16bits的SRAM芯片组成存储器模块组,多可缓存两帧XGA视频 图像。具体电路设计方法为:三片SRAM 的数据总线并行扩展为48位,地址总线和片选等控制信号全部相同,组成1M×48bits的大容量存储器,可满足系统要求。

4 FPGA逻辑设计FPGA是系统功能实现的模块。按照自顶向下的模块化设计思想,FPGA 内部功能逻辑可分为两大部分:1024×768@29.18Hz格式信号转换模块,320×256@50Hz格式信号转换模块。FPGA所有逻辑均使用 Verilog HDL语言在QuartusⅡ9.0平台下进行开发[7].

4.1 1024×768@29.18Hz格式信号转换模块模块实现了DVI接口1024×768@60Hz格式信号到CameraLink接口 1024×768@29.18Hz格式信号的转换。模块采用交替异步读写外部SRAM 组的方法,充分利用FPGA的并行工作能力,不涉及任何算法,实现了两种格式信号间60Hz到29.18Hz的帧频转换。模块结构如图3所示。

由图3可知,该模块功能逻辑包括以下部分:DVI接口逻辑,Camera Link接口逻辑,数据缓冲器,地址发生器,外存控制器。DVI接口逻辑接收解码器输出的数字视频信号,使地址发生器产生相应的RAM1写地址,并对 RAM1进行乒乓操作,将像素数据连续的写入双口缓冲器RAM1中。当RAM1半满或全满时,外存控制器产生写外部SRAM 操作,将像素数据从RAM1读出,缓存于外部SRAM;与此同时,CameraLink接口逻辑利用计数器产生帧行有效信号,使地址发生器产生相应的 RAM2读地址,并对RAM2进行乒乓操作,连续的从双口缓冲器RAM2中读取像素数据。当RAM2半空或全空时,外存控制器产生读外部SRAM 操作,将像素数据从SRAM 读出,缓存于双口RAM2.

外存控制器总是优先于读SRAM 操作,即双口RAM2半空或全空时,必然产生读外部SRAM 操作。当外存控制器执行写外部SRAM 操作时,若产生了读外部SRAM 操作,则写操作被中断且当前的写SRAM 地址被保存,读操作完成后,写操作从下一个写地址接着执行;否则写操作正常执行。经示波器测量,外存控制器产生的SRAM 读写信号时序图如图4所示。图4中,上方波形为SRAM 写信号,下方波形为SRAM 读信号,读写信号均为低电平有效。由图可知,第二次写操作执行过程中,产生了读操作。外存控制器将写信号置高而中断了写操作,读操作完成后,接着执行 写操作。

经过外存控制器,外部存储器中存储着当前的一帧DVI输入视频数据,且像素数据的存储地址与像素点在屏幕中的行列位置一一对应。Camera Link接口逻辑在其帧行有效信号的同步下,通过数据缓冲器RAM2将像素数据从外部存储器中读出,送给Camera Link发送器,便实现了视频格式转换。

Camera Link接口逻辑和DVI接口逻辑采用完全异步的像素时钟,两个模块并行工作。经示波器测量,得出帧同步信号转换时序图如图5所示。图5中,上方波形为输 入的DVI接口60Hz帧同步信号,下方波形为转换后输出的Camera Link接口29.18Hz帧同步信号。FPGA 使用帧同步信号清零地址发生器,可使显示出的视频图像平滑无跳动。

4.2 320×256@50Hz格式信号转换模块

模块实现了DVI接口1024×768@60Hz格式信号到CameraLink接口320×256@50Hz格式信号的转换。模块不进行外部存储器的读写,仅对输入视频信号进行同步处理和转换,模块结构框图如图6所示。

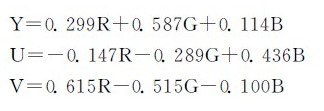

由图6可知,模块功能逻辑包括RGB到YUV转换逻辑,帧频转换逻辑,分辨率转换逻辑。系统输入的DVI视频信号基于RGB色度空间,而本模块输出信号则为基于YUV色域的黑白信号,RGB与YUV相互转换遵循以下公式:

RGB转YUV 逻辑对像素数据进行乘加处理完成色域转换,并去除UV信号,保留亮度分量Y信号进行24位扩展,便得到黑白图像信号;帧频转换逻辑对输入的DVI帧同步信 号计数,每6帧视频信号内,丢弃其1帧,可实现60Hz到50Hz的帧频转换;分辨率转换逻辑对输入像素信号进行均匀抽取,即每3行抽取1行,每3个 像素点抽取1个像素点,经FPGA的逻辑分析仪测量,得出抽取时序图如图7所示。

5 结束语

本文介绍的视频接口转换系统,选用专用视频接口芯片进行差分信号的编解码,以高性能FPGA 为功能,实现了两种接口不同格式视频信号的转换。系统充分利用FPGA 逻辑资源丰富、并行工作能力强等优势,不采取任何图像处理算法,便实现了帧频转换、分辨率转换及色度空间转换功能,大大缩短了系统研发周期。经 Camera Link采集显示系统验证,转换后的视频图像显示效果良好,完全满足某型仿真测试设备的视频信号转换要求。

下一篇:高数模转换器的温漂研究

版权与免责声明

凡本网注明“出处:维库电子市场网”的所有作品,版权均属于维库电子市场网,转载请必须注明维库电子市场网,https://www.dzsc.com,违反者本网将追究相关法律责任。

本网转载并注明自其它出处的作品,目的在于传递更多信息,并不代表本网赞同其观点或证实其内容的真实性,不承担此类作品侵权行为的直接责任及连带责任。其他媒体、网站或个人从本网转载时,必须保留本网注明的作品出处,并自负版权等法律责任。

如涉及作品内容、版权等问题,请在作品发表之日起一周内与本网联系,否则视为放弃相关权利。

- 锁相环的基本概念2024/4/23 17:56:14

- 信号与系统分析简介2024/4/16 17:03:33

- 使用逻辑信号、交流耦合和接地栅极驱动 CMOS 图腾柱2024/4/10 16:54:32

- 什么是射频?什么是射频信号?2024/4/7 17:53:28

- 探索光耦合器替代方案2024/3/29 17:04:49