I2C 有源上拉可节省电量

出处:网络整理 发布于:2024-06-13 15:54:52

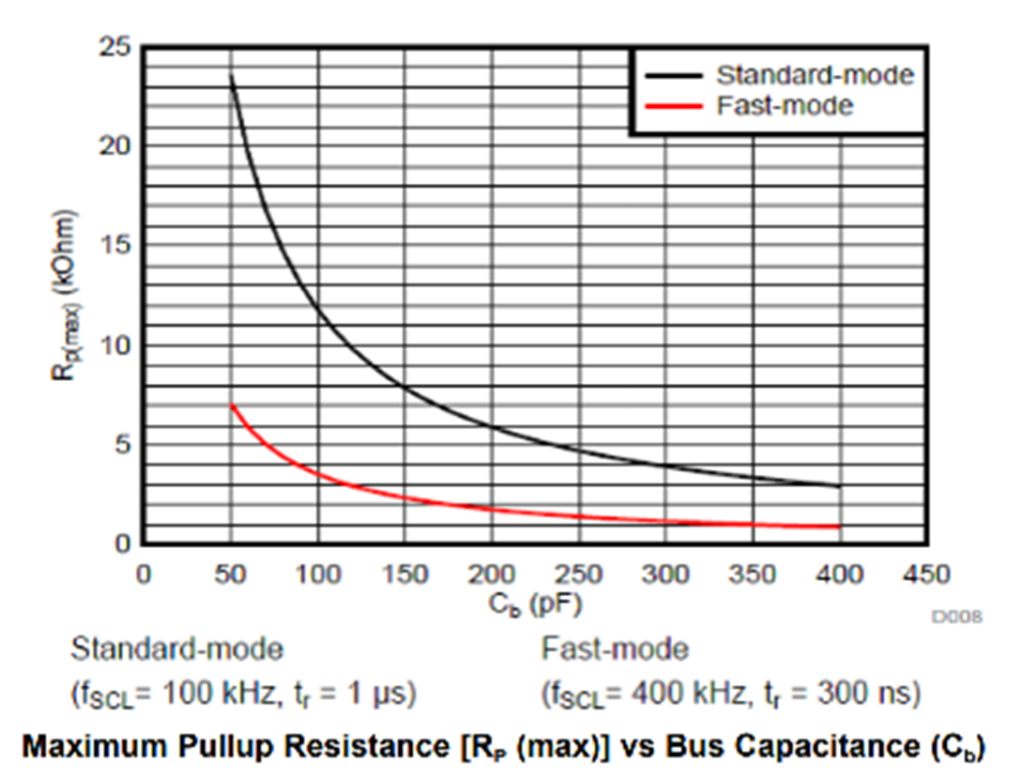

流行的 I 2 C 通信标准仅使用一条非常简单的两针总线(SCL 和 SDA)即可实现灵活的串行 I/O。它通过双向时序和数据流实现了这一技巧。双向流有利于节省引脚,但由于使用无源上拉电阻,因此不太适合节省功率。总线上拉电阻必须选择得足够低(从而通过足够的电流),以便以所选数据速率决定的速度对寄生总线电容进行充电。图 1说明了这种不方便的算法。

被动“上拉”过程中消耗的V/R电流量和V 2 /R功率取决于总线电容、上拉电压和占空比;如图 1 所示,对于快速模式 400 kHz、V = 5 V 和 Cb = 400 pF,消耗的电流量可能高达5V/1k = 5 mA和5 2 /1k = 25 mW。这很容易占到整个系统功耗的很大一部分。

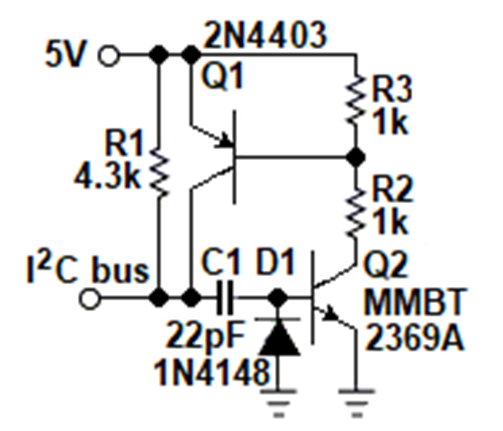

图 2再生有源上拉电路(需要两个电路之一),其值是根据图 1 所示的坏情况组合选择的。

这种简单的电路拓扑结构,虽然宣称其目的是为了节省上拉功率,但其起点并不高:无源上拉电阻 R1。整个电路的工作原理如图3所示。

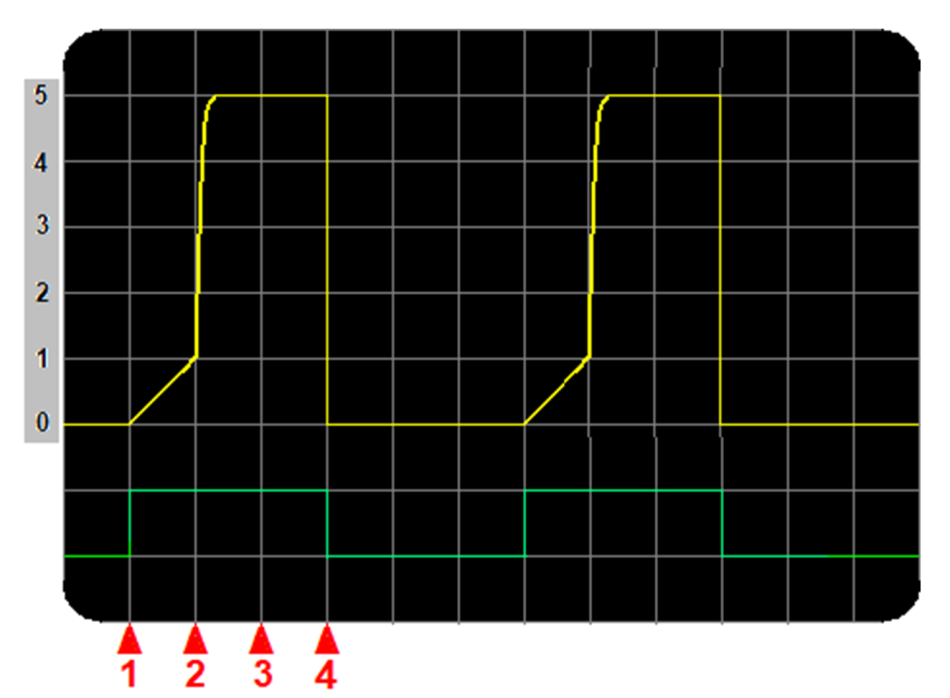

有源上拉过程分为四个步骤。

释放相关总线信号线(即 SCL 或 SDA)可使 R1 开始被动上拉并开始为总线电容充电。由此产生的电压上升很慢,因为 R1 比图 1 中按需要计算的 1k 大 4 倍多。显然,它永远无法足够快地完成上升时间!

但请稍等:产生的信号由 C1 耦合到 Q2 的基极。因此,在过程的第 2 步,Q2 导通,带动 Q1 导通,并启动一个非常快速的正反馈回路,该回路驱动两个晶体管进入饱和状态,并在数十纳秒内完成总线电容充电;消除 R1 上的压降并结束其功耗。

22 pF C1 的时间常数非常短,它作用于 Q2 的基极阻抗,使 C1 放电并终止晶体管的驱动,从而使它们开始关闭并结束有源上拉。这为 Q1 和 Q2 提供了从饱和状态恢复的时间。

下拉开始总线活动的下一个周期并通过 D1 对 C1 重新充电,这也可以保护 Q2 有限的(仅 4.5 V)反向 Vbe 额定值。

版权与免责声明

凡本网注明“出处:维库电子市场网”的所有作品,版权均属于维库电子市场网,转载请必须注明维库电子市场网,https://www.dzsc.com,违反者本网将追究相关法律责任。

本网转载并注明自其它出处的作品,目的在于传递更多信息,并不代表本网赞同其观点或证实其内容的真实性,不承担此类作品侵权行为的直接责任及连带责任。其他媒体、网站或个人从本网转载时,必须保留本网注明的作品出处,并自负版权等法律责任。

如涉及作品内容、版权等问题,请在作品发表之日起一周内与本网联系,否则视为放弃相关权利。

- 拥有点云数据的能否取代激光雷达?2025/8/11 16:25:52

- CAN XL 通信技术在车载毫米波雷达中的应用 (2)2025/8/8 16:24:00

- 光纤线和网线有啥区别2025/8/7 17:21:57

- 网线怎么排2025/8/1 11:42:44

- 全面对比:光纤线与网线的差异大揭秘2025/7/30 17:00:38