电动机驱动器中的DV/DT验证

出处:网络整理 发布于:2025-03-21 16:28:15

如果电机相(以下简称DV/DT)的电压的边缘陡度太高,则可能会通过电动机绕组的部分放电造成绕组的损害。该行业中广泛使用的极限值为5 kV/μs。限制值必须遵守并检查以保护电动机。虽然这通常是在开发过程中通过实验室进行双脉冲测试在开发过程中执行的,但本文重点介绍了在实际操作条件下终应用的测试。

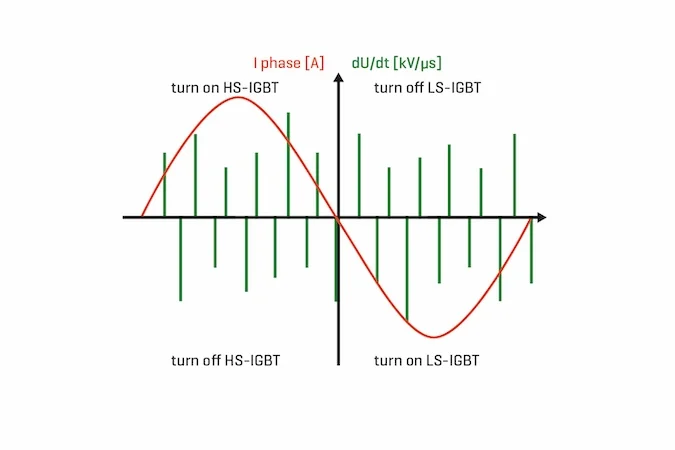

重要的是要了解一个阶段当前时期内有许多不同的边缘。在50 Hz相电流和2 kHz开关频率下,有80个不同的边缘,包括40个正和40个负。在16 kHz时,已经有640个边缘需要针对每个负载条件进行评估。因此,需要快速测量方法,因为对时间域中每个单个边缘的手动评估太耗时了。

边缘及其分布在相位周期内的陡度主要取决于功率半导体及其门电阻。其他次要影响因素包括电动机负荷,耗尽时间(软切换),相位电流方向,相位电流幅度,功率因数,PWM类型(脉冲宽度调制),二极管snappiness,电缆的类型和长度,半导体的温度,半导体的温度以及电路板和电动板和电源模块的布局。

如何确定DV/DT?

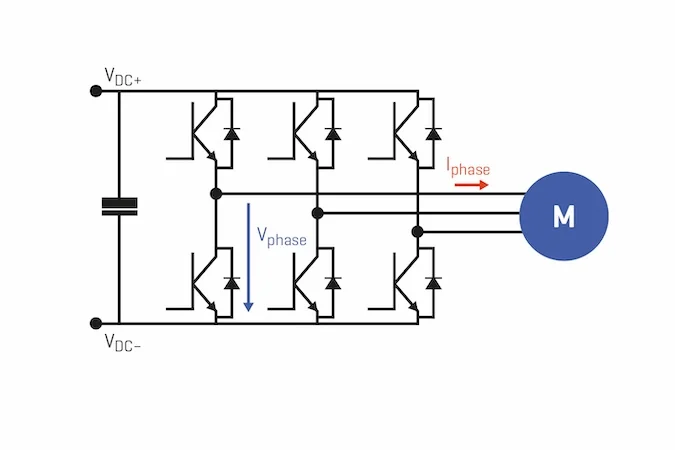

以示波器记录以下两个参数:

a)相电流

b)切换相电压

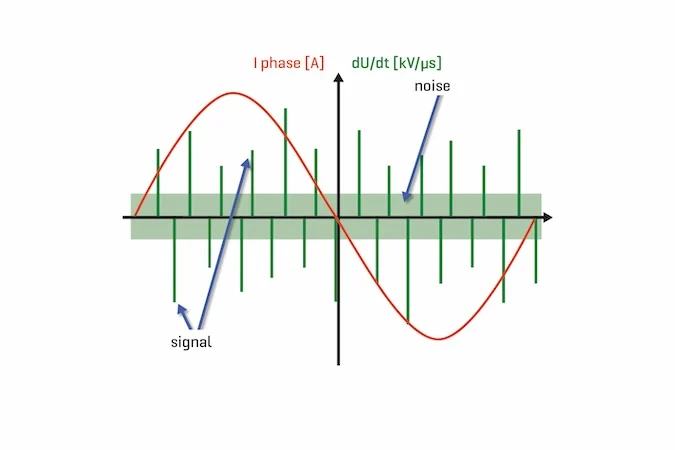

进入振幅域的转换具有直接在y轴上读取结果的优点。因此,不再需要对时间域中每个边缘的费力评估。

数学频道的公式:

\ [\ frac {kv} {\ mu s} = derivative(phase \,电压)\ times10^{ - 9} s \]

选择测量周期很有用,以便在示波器上完全显示相位电流的一个完整周期。这意味着可以将特定操作状态的所有边缘记录在单镜头中。

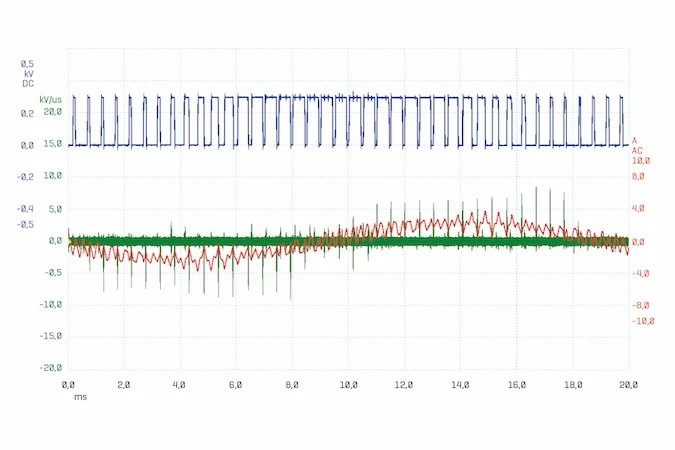

评估测量结果

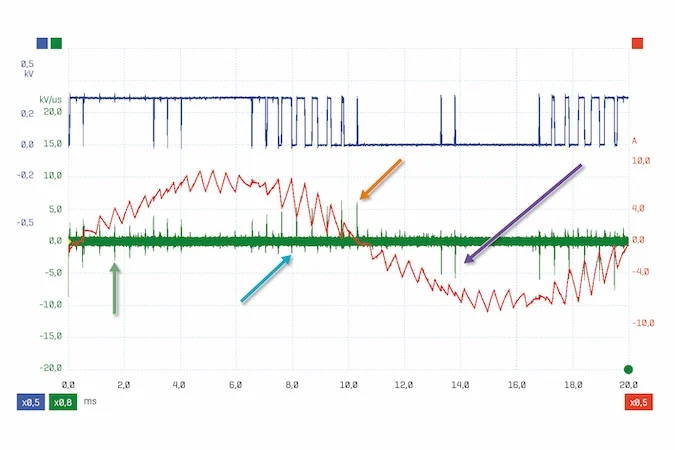

DV/DT可以直接从数学频道读取。无论一个周期的所有边缘都在设定的限制之内还是超过限制值(图2中的绿色尖峰),都可以看一见。

图像由Bodo的Power Systems

CH2 =相电流

MC = DV/DT

如果将5 kV/μs的极限值作为上述示例中的参考,则可以立即看到该极限值已显着超过相位电流的零交叉面积。

图3和4显示了(a)下降和(b)上升边缘的特写镜头。您可以清楚地看到DV/DT计算如何映射真正的边缘。

图像由Bodo的Power Systems [PDF]提供

CH2 =相电流

MC = DV/DT

图像由Bodo的Power Systems [PDF]提供

CH2 =相电流

MC = DV/DT

边缘/IGBT分配

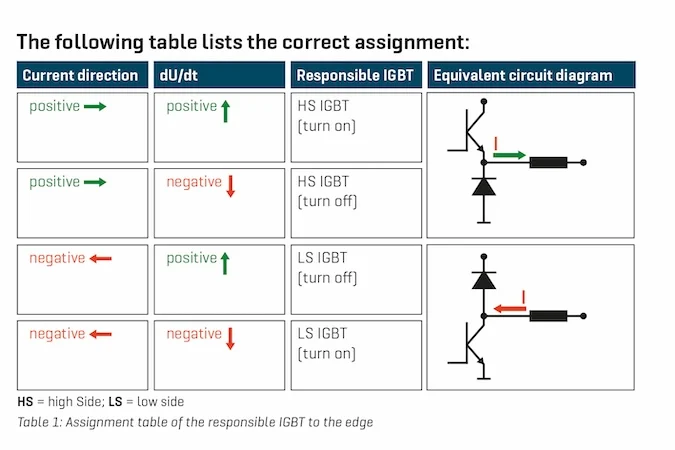

如果边缘陡度太高,则必须对其进行优化。在简单的情况下,可以调整门电阻。为了优化,每个陡峭的边缘都必须分配给负责任的IGBT(绝缘栅极双极晶体管)及其开关方向。简单地说:您必须知道HS(高侧)还是LS(低侧)IGBT负责,以及当前是否正在打开或关闭它。分配需要(a)相位电流方向和(b)DV/DT方向的情况分化。

下表列出了正确的分配:

表1。 负责的IGBT的分配表到边缘。图像由Bodo的Power Systems [PDF]提供图5以图形形式说明了上表的内容。

图5。 图形表示:负责的IGBT分配到相应的边缘。图像由Bodo的Power Systems [PDF]提供下面给出了一个实际的例子。图6说明了平面PWM开关逆变器的IGBT的分配。

CH2 =相电流

MC = DV/DT

橙色箭头:dv/dt =正&阶段电流=阳性=>打开HS IGBT紫色箭头:DV/DT =负&阶段电流=负=>打开LS IGBTTurquoise Arrow:DV/DT =负和相位电流=阳性=>关闭HS IGBT绿色箭头:没有边缘;即,这是来自相邻阶段的陡峭的电容耦合。

注意:随着电动机相之间的快速边缘和高电容耦合,发生了串扰现象。这些通过相电压的陡峭脉冲可见,因此也通过此处介绍的方法评估。但是,这并不是至关重要的,因为出于物理原因,串扰现象不能比边缘本身更陡峭。如有疑问,缩放进行测量将提供有关它是边缘还是串扰现象的信息。

表1中的等效电路图的注释

为相位的半桥绘制等效电路图可以简化对换向行为的解释,因为每个等效电路图仅包含一个活动的IGBT。如果相位电流为正,则相位的半桥作为降压阶段,如果相位电流为负,则作为增强阶段。因此,一个相的半桥可以分解为两个等效电路图,即分为(a)降压阶段和(b)增强阶段。这样,二极管模拟了相反的IGBT的抗平行二极管,该二极管在死亡时间内始终是导电性的。 (前提条件:非间隙操作,几乎总是存在于逆变器操作中)。

提高测量质量必须克服许多障碍才能取得良好的结果,因为计算出的DV/DT的质量和准确性在很大程度上取决于数学通道的噪声。它发生在计算过程中,而不是信号噪声!

注意:计算出的DV/DT的准确性很大程度上取决于噪声。

计算的DV/DT =(DV +噪声)÷DT

为了适当的结果,噪声必须明显小于开关边缘的DV/DT(信噪比)。因此,重要的是要知道噪声的来源以及如何将其保持在限度。

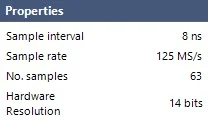

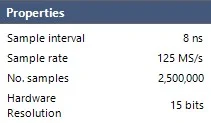

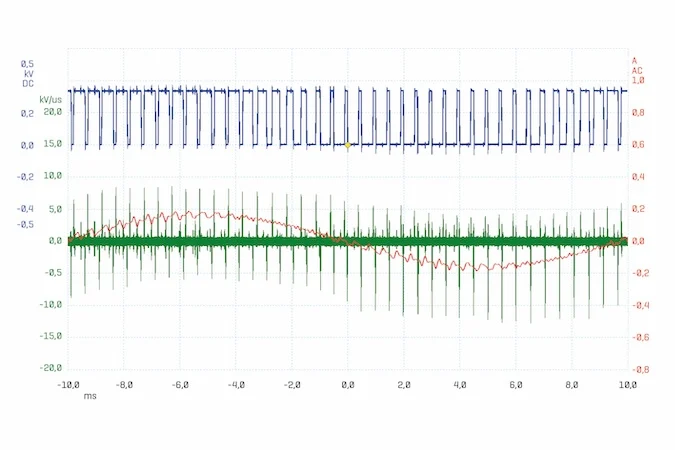

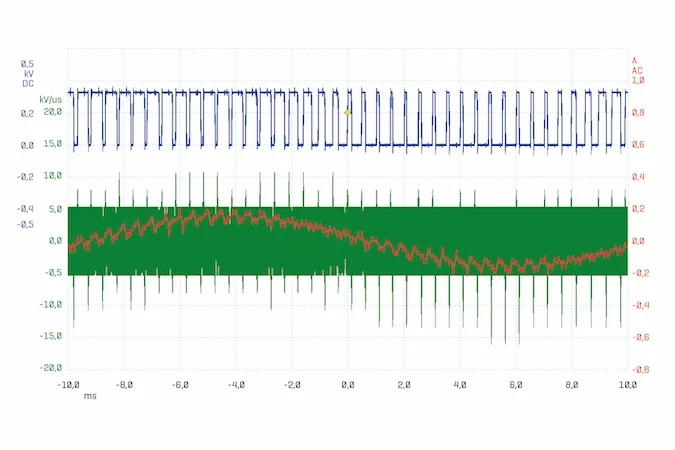

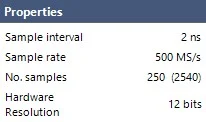

以下比较说明了较高的AD分辨率和更长的采样时间如何减少噪声。比较以下测量设置:

a)15位AD分辨率 / 8 NS采样时间(图8)

b)8位AD分辨率 / 2 NS采样时间(图9)

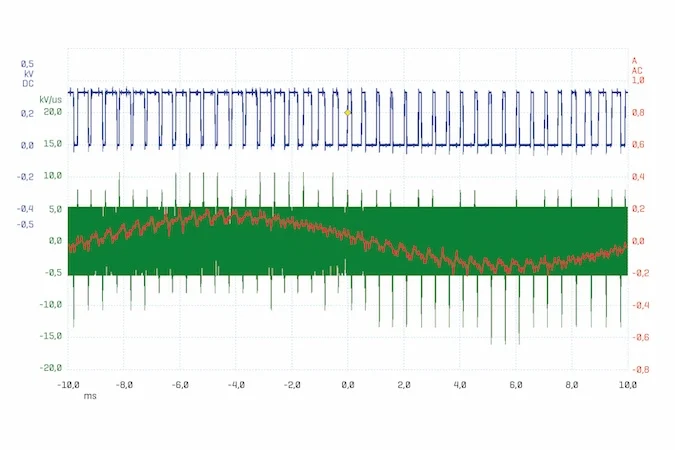

图8显示,高广告分辨率(15位)和长采样时间(8 ns)导致低噪声。

CH1 =针对DC的相电压

CH2 =相电流(过滤)

MC = DV/DT

图9显示,低的AD分辨率(8位)和短采样时间(2 ns)导致高噪声。噪声的差异清晰可见。在图9中,噪声甚至高于经常使用的极限值(> 5kV/μs),因此对于此限值测量值是无法使用的。

图9。 具有8位 / 2 NS的高噪声

CH1 =针对DC的相电压

CH2 =相电流(过滤)

MC = DV/DT

数学频道中的噪音在哪里?

原因本质上是示波器AD转换器的量化噪声。它会导致高频振幅误差。它在数学通道的分化过程中导致DV/DT误差。数学通道中的噪声是所有DV/DT误差的序列,并且量化误差(AD分辨率和测量范围)越大,并且采样时间越短(速率)。

选择合理的抽样时间

随着采样率的增加,噪声增加,结果质量降低。

因此,有必要选择合理的采样时间。采样时间必须(a)足够长以保持噪声足够低,并且(b)足够短,以确保用足够的分辨率对边缘进行采样。

一个良好的妥协是选择一个抽样时间,该抽样时间在边缘内创建大约3个测量段(4个样本)。

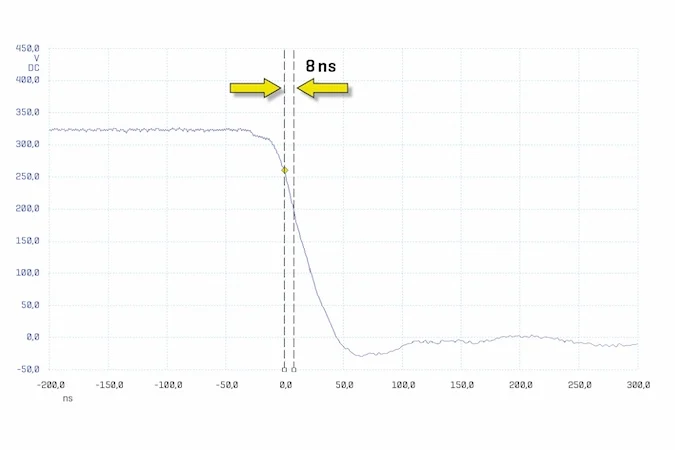

例如,在32 ns边缘时间(80% / 20%)的采样率应约为8 ns。

这在图10中说明了。光标之间的时间对应于8 ns,因此等于明智的采样时间。在边缘内测量了三个不同的部分。边缘采样得很好。这是采样时间和噪声之间的良好折衷,并导致良好的信噪比。

图10。 边缘长度v。抽样时间

CH1 =相电压

下一篇:解剖电机故障

版权与免责声明

凡本网注明“出处:维库电子市场网”的所有作品,版权均属于维库电子市场网,转载请必须注明维库电子市场网,https://www.dzsc.com,违反者本网将追究相关法律责任。

本网转载并注明自其它出处的作品,目的在于传递更多信息,并不代表本网赞同其观点或证实其内容的真实性,不承担此类作品侵权行为的直接责任及连带责任。其他媒体、网站或个人从本网转载时,必须保留本网注明的作品出处,并自负版权等法律责任。

如涉及作品内容、版权等问题,请在作品发表之日起一周内与本网联系,否则视为放弃相关权利。

- 直流电动机的工作原理/直流发电机的工作原理2025/8/11 17:07:01

- 工业充电器隔离式 DC - DC 功率级拓扑结构选型基础2025/8/11 16:41:27

- 单相异步电动机是什么?具有什么特征?2025/8/8 16:42:39

- IGBT 短路振荡机制的深度解析2025/8/8 16:16:56

- 工业充电器隔离式 DC - DC 功率级拓扑结构选型全解析2025/8/7 16:40:14