在这篇产品操作方法文章中,IDT 的 Fred Hirning 描述了在处理基于 FPGA 的高速通信接口(例如 SerDes)中的时钟抖动时所面临的问题,以及外部锁相环 (PLL)(例如公司的 VersaClock5)如何处理FemtoClock NG时钟发生...

时间:2023-03-14 阅读:417 关键词: FPGA 通信接口

出于鲁棒性、安全性、高共模电压考量,或为了消除可在测量中带来误差的接地环路,许多数据采集(DAQ)应用都需要隔离DAQ信号链路径。ADI的精密高速技术使系统设计人员能够...

时间:2022-03-16 阅读:449 关键词:计算隔离式精密高速DAQ的采样时钟抖动的简单步骤DAQ

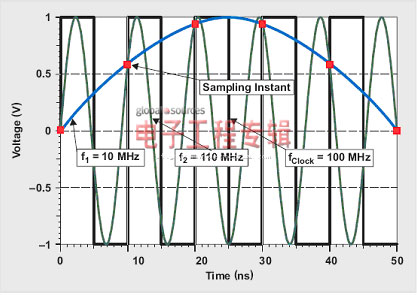

新型的高速ADC都具备高模拟输入带宽(约为采样频率的3到6倍),因此它们可以用于许多欠采样应用中。ADC设计的进展极大地扩展了可用输入范围,这样系统设计人员便可以去掉至...

分类:模拟技术 时间:2012-03-21 阅读:4274 关键词:准确地估算采样时钟抖动的方法分析

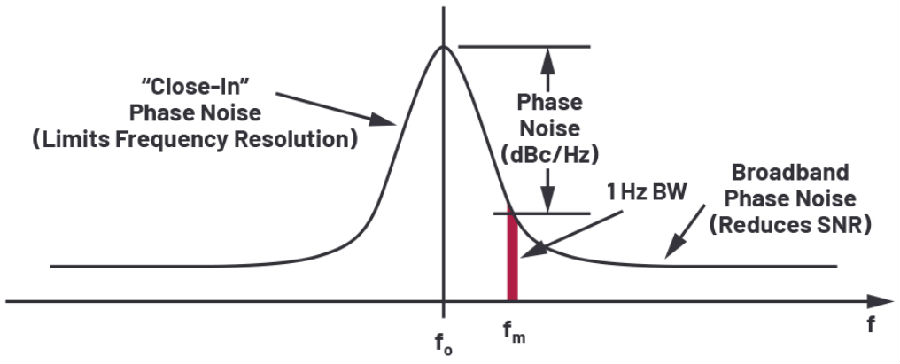

引言 用于在更远距离对日益增长的海量数据进行传输的一些标准不断出现。来自各行业的工程师们组成了各种委员会和标准机构,根据其开发标准的目标(数据吞吐量和通信距离)确定抖动预算;同时还要考虑到组成通信链...

分类:其它 时间:2011-05-25 阅读:1871 关键词:简析信号链基础的时钟抖动问题

摘要: 从ADC 的输入信号及时钟源的自身参数着手, 主要分析了输入信号幅值、频率、采样频率对时钟抖动及ADC 信噪比的影响,根据ADC 手册数据提供的信息给出了时钟抖动的计...

分类:模拟技术 时间:2011-03-17 阅读:3222 关键词:高速ADC时钟抖动及其影响的研究ADS5500

随着新一代串行数据标准成功地从快速过渡到超高速,设计人员需要花费大量时间考虑这些高速信号的模拟设计,只是简单关注1、0数字域信号远远不能满足实际要求。为了找到潜在的问题并加以解决,从而避免现场应用出现这...

分类:通信与网络 时间:2010-08-17 阅读:1790 关键词:消除高速串行链路的时钟抖动串行链路时钟抖动