24LC65

3.6

Device Addressing

4.0

4.1

WRITE OPERATION

Byte Write

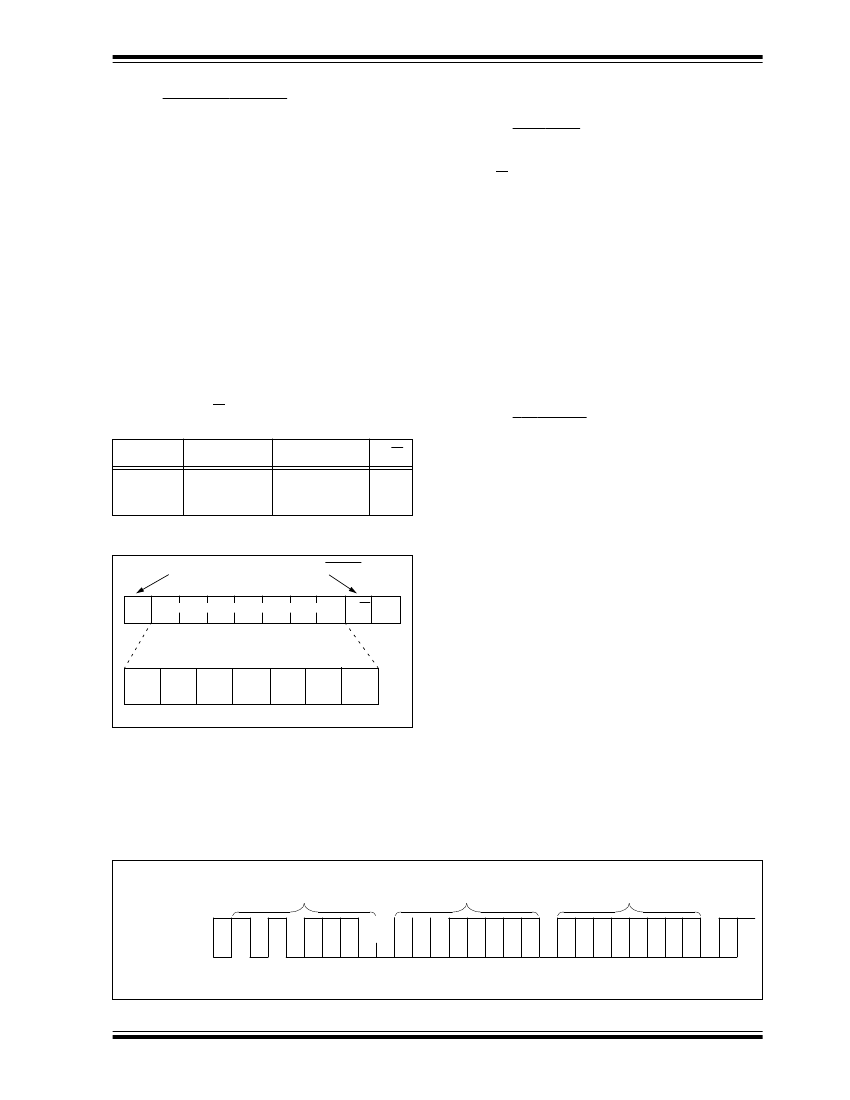

A control byte is the 铿乺st byte received following the

start condition from the master device. The control byte

consists of a four bit control code, for the 24LC65 this is

set as 1010 binary for read and write operations. The

next three bits of the control byte are the device select

bits (A2, A1, A0). They are used by the master device

to select which of the eight devices are to be accessed.

These bits are in effect the three most signi铿乧ant bits of

the word address. The last bit of the control byte de铿乶es

the operation to be performed. When set to a one a

read operation is selected, when set to a zero a write

operation is selected. The next two bytes received

de铿乶e the address of the 铿乺st data byte (Figure 4-1).

Because only A12..A0 are used, the upper three

address bits must be zeros. The most signi铿乧ant bit of

the most signi铿乧ant byte is transferred 铿乺st. Following

the start condition, the 24LC65 monitors the SDA bus

checking the device type identi铿乪r being transmitted.

Upon receiving a 1010 code and appropriate device

select bits, the slave device (24LC65) outputs an

acknowledge signal on the SDA line. Depending upon

the state of the R/W bit, the 24LC65 will select a read

or write operation.

Operation Control Code

Read

Write

1010

1010

Device Select

Device Address

Device Address

R/W

1

0

Following the start condition from the master, the con-

trol code (four bits), the device select (three bits), and

the R/W bit which is a logic low is placed onto the bus

by the master transmitter. This indicates to the

addressed slave receiver (24LC65) that a byte with a

word address will follow after it has generated an

acknowledge bit during the ninth clock cycle. Therefore

the next byte transmitted by the master is the high-order

byte of the word address and will be written into the

address pointer of the 24LC65. The next byte is the

least signi铿乧ant address byte. After receiving another

acknowledge signal from the 24LC65 the master device

will transmit the data word to be written into the

addressed memory location. The 24LC65 acknowl-

edges again and the master generates a stop condi-

tion. This initiates the internal write cycle, and during

this time the 24LC65 will not generate acknowledge

signals (Figure 4-1).

4.2

Page Write

FIGURE 3-2:

START

CONTROL BYTE

ALLOCATION

READ/WRITE

SLAVE ADDRESS

R/W

A

1

0

1

0

A2

A1

A0

The write control byte, word address and the 铿乺st data

byte are transmitted to the 24LC65 in the same way as

in a byte write. But instead of generating a stop condi-

tion the master transmits up to eight pages of eight data

bytes each (64 bytes total) which are temporarily stored

in the on-chip page cache of the 24LC65. They will be

written from the cache into the EEPROM array after the

master has transmitted a stop condition. After the

receipt of each word, the six lower order address

pointer bits are internally incremented by one. The

higher order seven bits of the word address remain con-

stant. If the master should transmit more than eight

bytes prior to generating the stop condition (writing

across a page boundary), the address counter (lower

three bits) will roll over and the pointer will be incre-

mented to point to the next line in the cache. This can

continue to occur up to eight times or until the cache is

full, at which time a stop condition should be generated

by the master. If a stop condition is not received, the

cache pointer will roll over to the 铿乺st line (byte 0) of the

cache, and any further data received will overwrite pre-

viously captured data. The stop condition can be sent

at any time during the transfer. As with the byte write

operation, once the stop condition is received an inter-

nal write cycle will begin. The 64 byte cache will con-

tinue to capture data until a stop condition occurs or the

operation is aborted (Figure 4-2).

FIGURE 4-1:

BUS ACTIVITY

MASTER

BYTE WRITE

S

T

A

R

T

CONTROL

BYTE

WORD

ADDRESS

DATA

S

T

O

P

SDA LINE

S

A

C

K

0 0 0

A

C

K

A

C

K

P

BUS ACTIVITY

漏

1996 Microchip Technology Inc.

DS21073E-page 5