DS1621

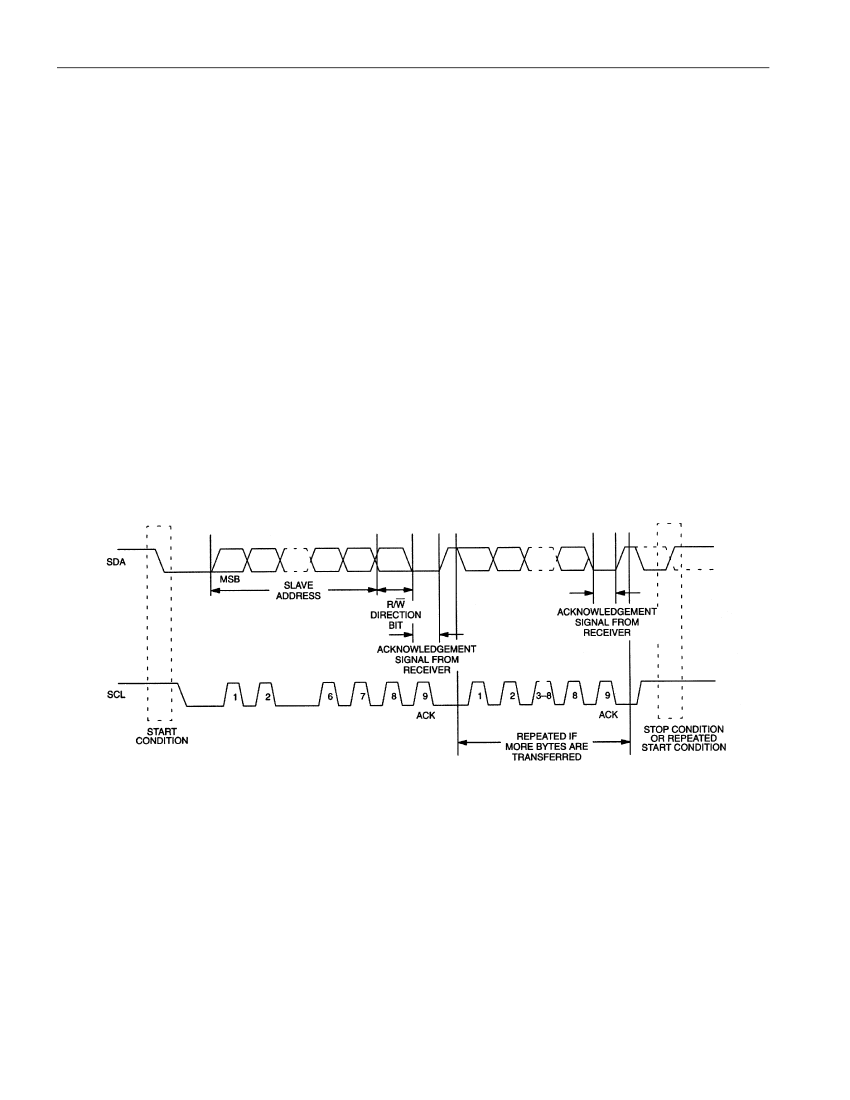

Data valid:

The state of the data line represents valid data when, after a START condition, the data line

is stable for the duration of the HIGH period of the clock signal. The data on the line must be changed

during the LOW period of the clock signal. There is one clock pulse per bit of data.

Each data transfer is initiated with a START condition and terminated with a STOP condition. The

number of data bytes transferred between START and STOP conditions is not limited and is determined

by the master device. The information is transferred byte鈥搘ise and each receiver acknowledges with a

ninth鈥揵it.

Within the bus specifications a regular mode (100 kHz clock rate) and a fast mode (400 kHz clock rate)

are defined. The DS1621 works in both modes.

Acknowledge:

Each receiving device, when addressed, is obliged to generate an acknowledge after the

reception of each byte. The master device must generate an extra clock pulse which is associated with this

acknowledge bit.

A device that acknowledges must pull down the SDA line during the acknowledge clock pulse in such a

way that the SDA line is stable LOW during the HIGH period of the acknowledge related clock pulse. Of

course, setup and hold times must be taken into account. A master must signal an end of data to the slave

by not generating an acknowledge bit on the last byte that has been clocked out of the slave. In this case,

the slave must leave the data line HIGH to enable the master to generate the STOP condition.

DATA TRANSFER ON 2鈥揥IRE SERIAL BUS

Figure 4

Figure 4 details how data transfer is accomplished on the 2鈥搘ire bus. Depending upon the state of the

R/W bit, two types of data transfer are possible:

1.

Data transfer from a master transmitter to a slave receiver.

The first byte transmitted by the

master is the slave address. Next follows a number of data bytes. The slave returns an acknowledge

bit after each received byte.

2.

Data transfer from a slave transmitter to a master receiver.

The first byte, the slave address,

is transmitted by the master. The slave then returns an acknowledge bit. Next follows a number of

data bytes transmitted by the slave to the master. The master returns an acknowledge bit after all

received bytes other than the last byte. At the end of the last received byte, a 鈥?acknowledge鈥?is

not

returned.

7 of 16

102299