www.ti.com

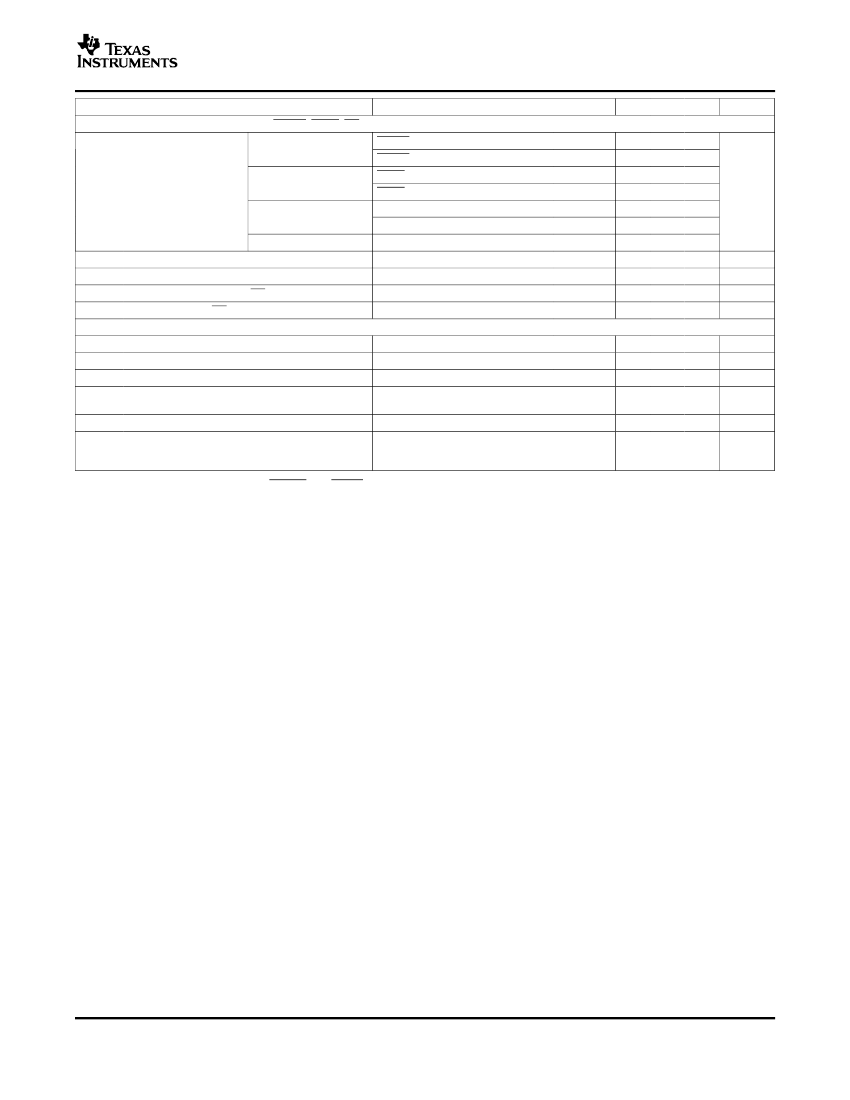

PARAMETER

LOGIC SECTION (CLOCK, DATA, LATCH, RESET, SHDN, OC)

I

I(/RESET)

(5)

TPS2220A, TPS2223A

TPS2224A, TPS2226A

SLVS428B 鈥?MAY 2002 鈥?REVISED SEPTEMBER 2004

TEST CONDITIONS

(1)

MIN

TYP

MAX

UNIT

RESET = 5.5 V

RESET = 0 V

SHDN = 5.5 V

SHDN = 0 V

LATCH = 5.5 V

LATCH = 0 V

0 V to 5.5 V

-1

-30

-1

-50

-20

1

-10

1

-3

50

碌A

I

I

Input current, logic

I

I(/SHDN) (5)

I

I(LATCH) (5)

I

I(CLOCK,

DATA)

-1

-1

2

1

1

V

0.8

V

V

碌A

V

IH

V

IL

V

O(sat)

I

lkg

V

I(3.3V)

V

hys(3.3V)

V

I(5V)

V

hys(5V)

t

df

V

I(POR)

High-level input voltage, logic

Low-level input voltage, logic

Output saturation voltage at OC

Leakage current at OC

I

O

= 2 mA

V

O(/OC)

= 5.5 V

3.3-V level below which all switches are Hi-Z

0.14

0

0.4

1

UVLO AND POR (POWER-ON RESET)

Input voltage at 3.3V pin, UVLO

UVLO hysteresis voltage at VA

(6)

Input voltage at 5V pin, UVLO

UVLO hysteresis voltage at 5V

(6)

Delay time for falling response, UVLO

(6)

Input voltage, power-on reset

(6)

3.3-V voltage below which POR is asserted causing a

RESET internally with all line switches open and all

discharge switches closed.

5-V level below which only 5V switches are Hi-Z

Delay from voltage hit (step from 3 V to 2.3 V) to

Hi-Z control (90% V

G

to GND)

2.3

2.4

2.7

100

2.5

100

4

1.7

2.9

V

mV

V

mV

碌s

V

(5)

(6)

LATCH has low-current pulldown. RESET and SHDN have low-current pullup.

Specified by design; not tested in production.

5