DC-DC的PCB设计需要注意哪些点?

出处:记得诚。 发布于:2022-12-30 16:14:08

01

Bad layout

EMI,DC-DC的SW管脚上面会有较高的dv/dt, 比较高的dv/dt会引起比较大的EMI干扰;

地线噪声,地走线不好,会在地线上面会产生比较大的开关噪声,而这些噪声会影响到其它部分的电路;

布线上产生电压降,走线太长,会使走线上产生压降,而降低整个DC-DC的效率;

02

一般原则

开关大电流回路尽量短;

信号地和大电流地(功率地)单独走线,并在芯片GND处单点连接;

① 开关回路短

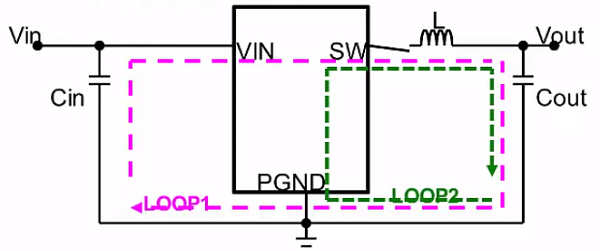

下图中红色LOOP1为DC-DC高边管导通,低边管关闭时的电流流向;绿色LOOP2的为高边管关闭,低边管开启时的电流流向;

为使这两个回路尽量小,引入更少的干扰,需要遵从如下几点原则:

电感尽量靠近SW管脚;

输入电容尽量靠近VIN管脚;

输入输出电容的地尽量靠近PGND脚;

使用铺铜的方式走线;

走线过细过长会增大阻抗,大电流在此大阻抗上会产生比较高的纹波电压;

走线过细过长会增大寄生电感,此电感上耦合开关噪声,影响DC-DC稳定性,造成EMI问题;

寄生电容和阻抗会增大开关损耗和导通损耗,影响DC-DC效率;

② 单点接地

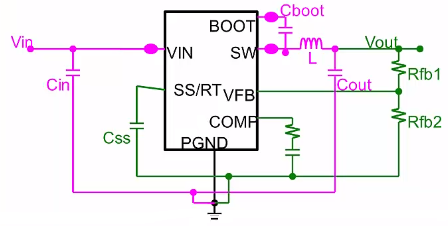

单点接地,指的是信号地和功率地进行单点接地,功率地上会有比较大的开关噪声,所以需要尽量避免对敏感小信号造成干扰,如FB反馈管脚。

大电流地:L,Cin,Cout,Cboot连接到大电流地的网络;

小电流地:Css,Rfb1,Rfb2单独连接到信号地的网络;

① 输入输出电容的GND用铜皮进行连接,摆件时,两者的地尽量放一起;

② DC-DC Ton和Toff时的电流路径都很短;

③ 右边小信号是单点接地,距离比较远,免受左边大电流开关噪声的影响;

图片

TI某开发板的DC-DC PCB layout

03

实例

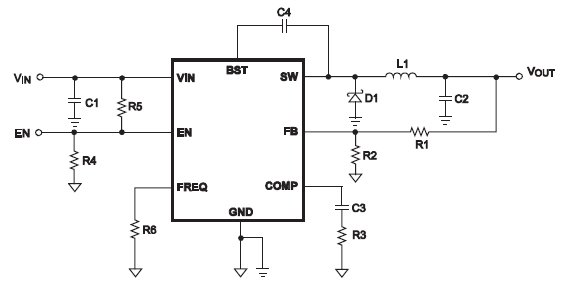

如下给出一个典型DC-DC BUCK电路的layout,SPEC中给出如下几点:

输入电容,高边MOS管,和续流二极管形成的开关回路尽可能小和短;

输入电容尽可能靠近Vin Pin脚;

确保所有反馈连接短而直接,反馈电阻和补偿元件尽可能靠近芯片;

SW远离敏感信号,如FB;

将VIN、SW,特别是GND分别连接到一个大的铜区,以冷却芯片,提高热性能和长期可靠性;

layout指导

04

小结一下

DC-DC电路的layout至关重要,直接影响到DC-DC的工作稳定性和性能,一般DC-DC芯片的SPEC都会给出layout指导,可参考进行设计。

今天的文章内容到这里就结束了,希望对你有帮助。

版权与免责声明

凡本网注明“出处:维库电子市场网”的所有作品,版权均属于维库电子市场网,转载请必须注明维库电子市场网,https://www.dzsc.com,违反者本网将追究相关法律责任。

本网转载并注明自其它出处的作品,目的在于传递更多信息,并不代表本网赞同其观点或证实其内容的真实性,不承担此类作品侵权行为的直接责任及连带责任。其他媒体、网站或个人从本网转载时,必须保留本网注明的作品出处,并自负版权等法律责任。

如涉及作品内容、版权等问题,请在作品发表之日起一周内与本网联系,否则视为放弃相关权利。

- 常用 PCB 接插件设计的关键要求解析2025/8/6 10:33:54

- 剖析 DC - DC 电路 SW 节点铺铜面积大小的利弊2025/8/4 15:58:53

- PCB 上光电元器件频繁失效的原因及分析2025/8/2 11:01:22

- 探究 PCB 上光电元器件失效的背后真相2025/8/2 10:56:23

- 1A和100A电流分别需要多大的PCB线宽2025/7/30 15:30:03