在数字电路设计中,时钟信号是在高电平和低电平状态之间振荡并指导电路性能的信号。逻辑可以在应用中的上升沿、下降沿或两个沿上切换。由于数以千计的实例在给定的时钟域上...

时间:2023-11-06 阅读:416 关键词:数字电路

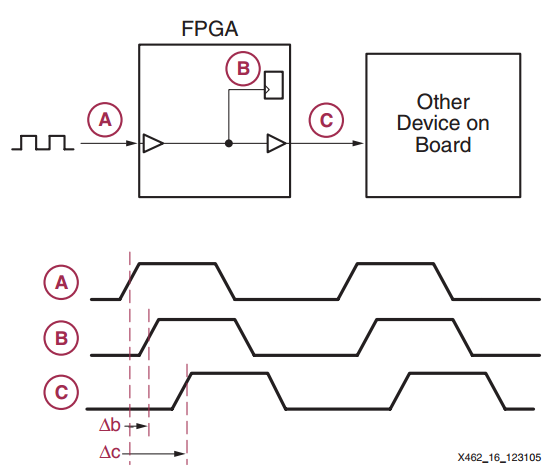

即使在小型数字设计中,时钟信号也可能被分发到整个系统中的数百个时钟元件。这些高扇出时钟信号负责同步系统的不同子系统或组件。这就是为什么我们需要仔细注意时钟网络的...

时间:2023-11-01 阅读:277 关键词:信号

高速传输系统 近年来,随着数字传输系统需要更大的容量,出现了用高速串行线路取代并行总线的趋势。虽然传输距离可能不到一米,但这种链路的设计与跨越几米甚至几十公里...

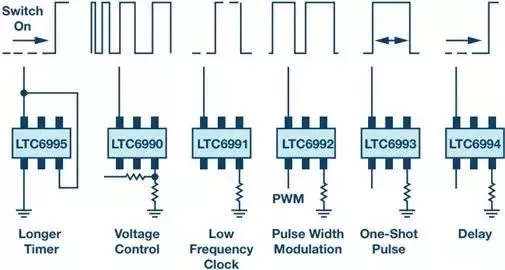

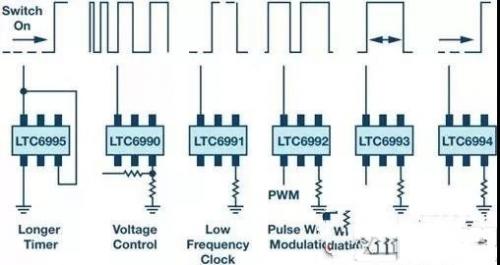

许多模拟电路需要一种时钟信号,或者要求能在一定时间后执行某项任务。对于这样的应用,有各种各样适用的方案。 1、555定时器 对于简单的时序任务,可以使用标准的55...

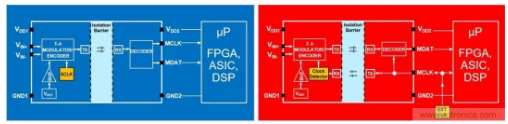

隔离的Σ-Δ调制器长期以来被证明可以在嘈杂的工业电机应用环境中提供非常高的和强劲的电流和电压感测能力。有两类隔离型Σ-Δ调制器:一种是在IC内部产生时钟信号;另一种...

许多模拟电路需要一种时钟信号,或者要求能在一定时间后执行某项任务。对于这样的应用,有各种各样适用的解决方案。 1、555定时器 对于简单的时序任务,可以使用标准...

锁相环是最通用的电路功能之一。它们用于为处理器提供时钟(相当良好的情况),以及用于在固定和调谐频率发送器和接收器中建立调谐。 然而,最困难的挑战之一是在无线链路中恢复,清理和重新计时定时信号。与处理器...

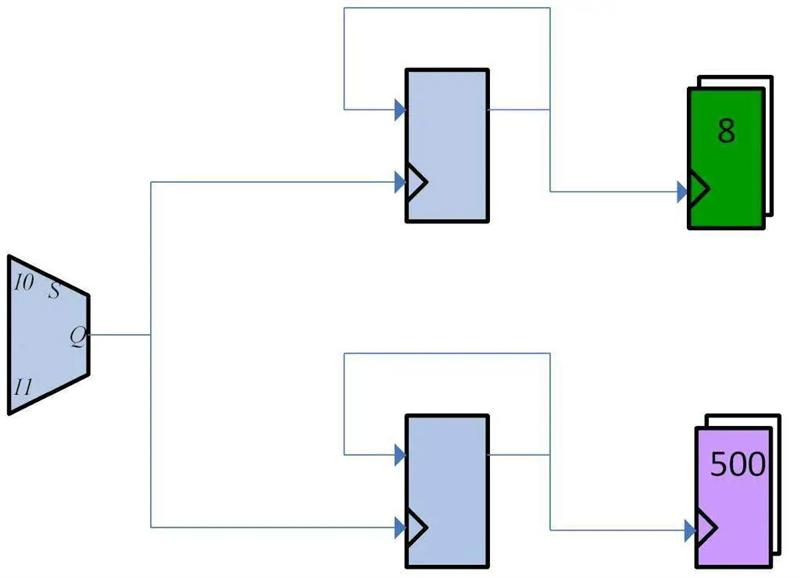

在数字电路设计中,是一种在高态与低态之间振荡的信号,决定着电路的性能。在应用中,逻辑可能在上升沿、下降沿触发,或同时在上升沿和下降 沿触发。由于溢出给定时钟域的...

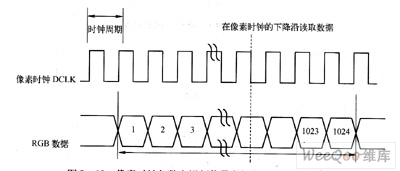

只要是数字信号处理电路,就必须有时钟信号。在液晶面板中,像素时钟是一个非常重要的时钟信号。像素时钟信号的频率与液晶面板的工作模式有关,液晶面板分辨率越高,像素时...

分类:光电显示/LED照明 时间:2009-06-16 阅读:5649 关键词:显示器信号

安森美NB3N3001 PLL时钟产生器带来抖动小于皮秒的LVPECL时钟信号

高能效电源管理解决方案供应商安森美半导体(ON Semiconductor)日前宣布扩充高性能时钟产生器产品系列,推出采用锁相环(PLL)技术的新系列PureEdge产品,带来抖动少于皮秒(ps...

- 英特尔数据存储如何操作和实现

- 什么是微动开关_微动开关有什么用_微动开关使用方法

- VCC,VDD,VEE,VSS在电源原理图中有什么区别?

- 低压配电系统设计规范_低压配电系统设计注意事项

- xEV 主逆变器电源模块中第四代 SiC MOSFET 的短路测试

- 光耦详细应用教程

- 定义绝缘耐久性评估的电压脉冲测试要求

- 采用沟槽MOS结构,使存在权衡关系的VF和IR相比以往产品得到显著改善 ROHM推出实现业界超快trr的100V耐压SBD“YQ系列”

- NOVOSENSE - 纳芯微推出车规级温湿度传感器NSHT30-Q1,助力汽车智能化发展

- Keysight - EV 电池设计创新:扩大续航里程、延长电池寿命