鈥?/div>

MULTIPLE OUTPUT

CLOCK SYNTHESIZER

Fully Integrated PLL

Fully Integrated Crystal Oscillator

Low cost, low jitter design

Low cost 8鈥搇ead SOIC packaging

In addition to the output clock frequencies, the MPC9108 also offers a

lock indicator output. When the internal PLL achieves phase and

frequency lock the CLK_LOCK signal will go HIGH. The pin will remain

HIGH unless the PLL loses lock due to input clock or power supply

disturbances.

The XTALIN pin (pin 1) can be over鈥揹riven with a standard 5V CMOS

signal. When an externally generated reference is used the XTALOUT pin

should be left open.

The MPC9108 operates from a 5.0V supply across the commercial

temperature range of 0掳C to 70掳C. The 8鈥搇ead SOIC package is used to

optimize board space efficiency as well as minimizing cost.

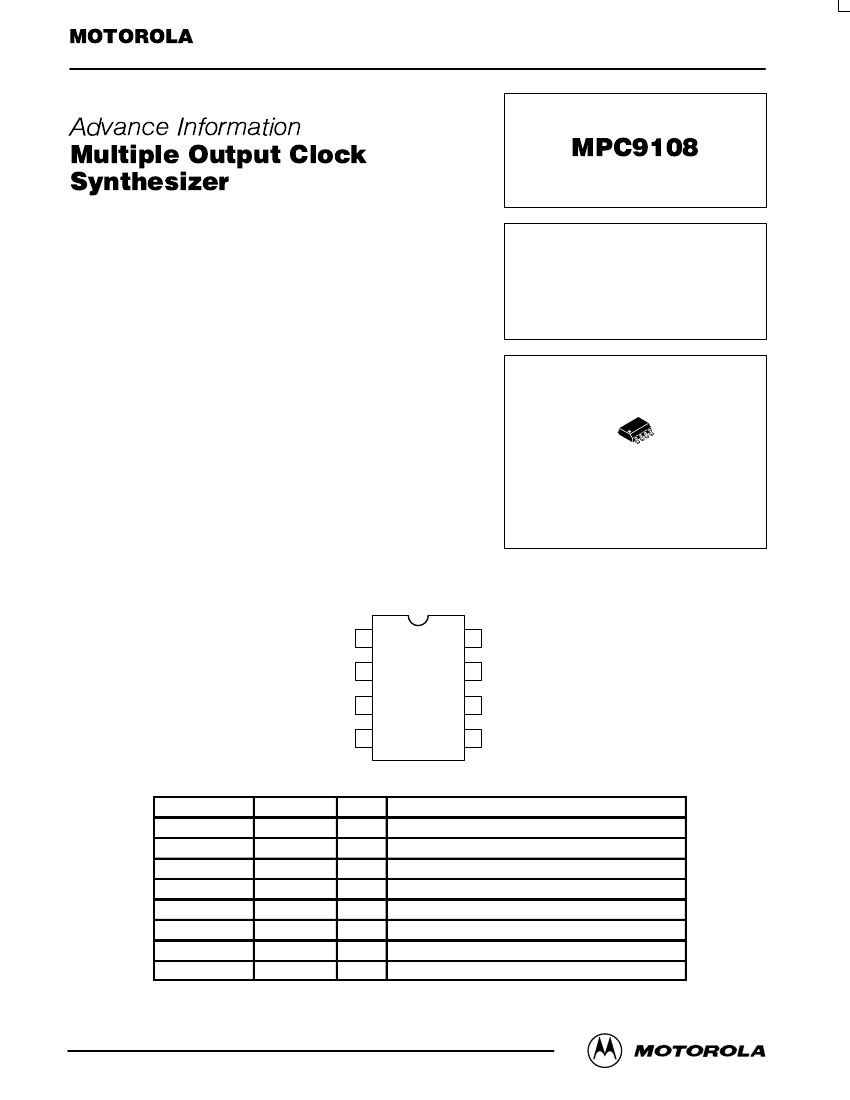

Pinout: 8鈥揕ead SOIC

(Top View)

XTALIN

VDD

GND

CLK1

1

2

3

4

8

7

6

5

XTALOUT

CLK_LOCK

CLK2

CLK3

D SUFFIX

PLASTIC SOIC

CASE 751鈥?3

Pin Descriptions

Pin Name

XTALIN

VDD

GND

CLK1

CLK2

CLK3

CLK_LOCK

XTALOUT

Pin Number

1

2

3

4

5

6

7

8

I/O

I

鈥?/div>

鈥?/div>

O

O

O

O

O

Function

20MHz Crystal Connection, External Reference Point

+5V Power Supply

Ground

20MHz Output, Buffer Xtal Output

50MHz Output, PLL Controlled

40MHz Output, PLL Controlled

HIGH When PLL is Locked

Crystal Oscillator Connection

This document contains information on a new product. Specifications and information herein are subject to

change without notice.

1/97

漏

Motorola, Inc. 1997

1

REV 0