鈥?/div>

100ps Cycle鈥搕o鈥揅ycle Jitter

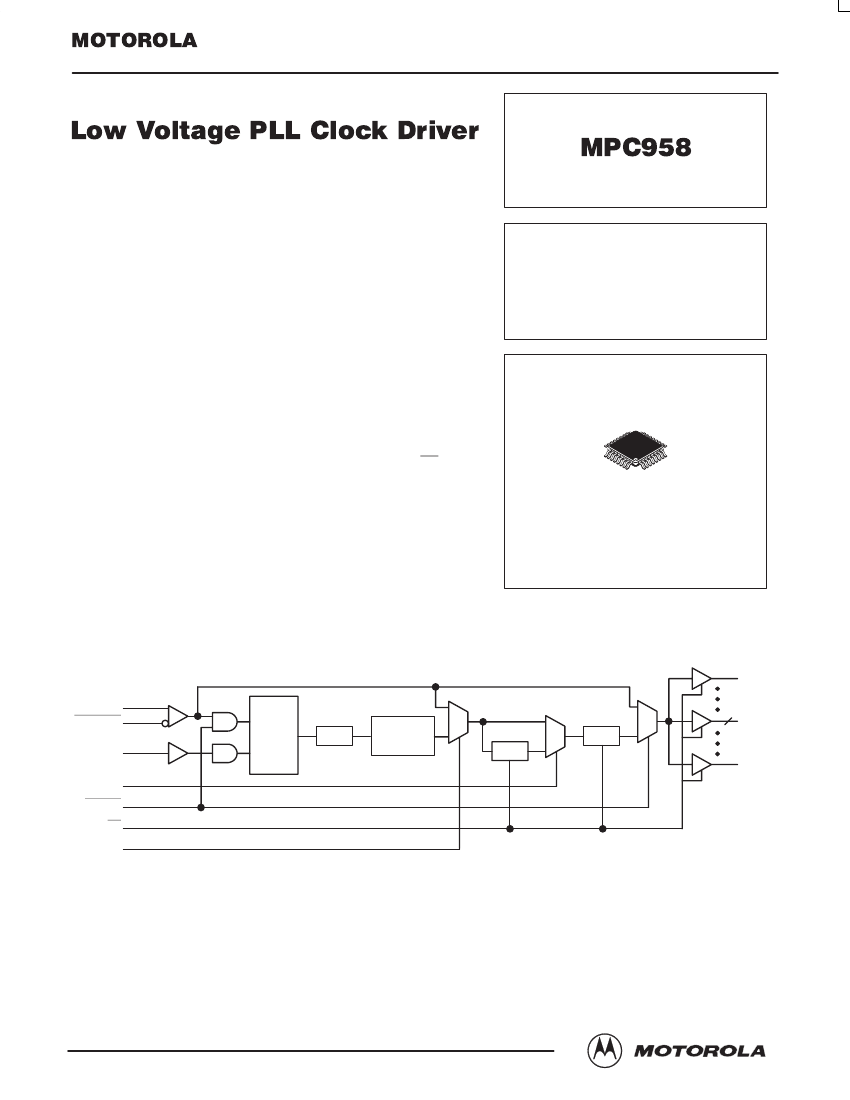

The MPC958 has a differential LVPECL reference input along with an

external feedback input. These features make the MPC958 ideal for use

as a zero delay, low skew fanout buffer. The device performance has

been tuned and optimized for zero delay performance. The MR/OE input

pin will tristate the output buffers when driven 鈥渉igh鈥?

The MPC958 is fully 3.3V compatible and requires no external loop

filter components. All control inputs accept LVCMOS or LVTTL

compatible levels while the outputs provide LVCMOS levels with the

ability to drive terminated 50鈩?transmission lines. For series terminated

50鈩?lines, each of the MPC958 outputs can drive two traces giving the

device an effective fanout of 1:22. The device is packaged in a 7x7mm

32鈥搇ead LQFP package to provide the optimum combination of board

density and performance.

FA SUFFIX

32鈥揕EAD LQFP PACKAGE

CASE 873A鈥?2

QFB

(Int pull up)

PECL_CLK

(Int pull down)

PECL_CLK

FB_CLK

VCO_SEL

BYPASS

MR/OE

PLL_EN

(Int pull up)

0

Phase

Detector

LPF

VCO

200鈥?00MHz

1

梅2

0

1

梅2

0

1

9

Q0:8

Q9

(Int pull up)

(Int pull up)

(Int pull down)

(Int pull up)

Figure 1. Logic Diagram

06/00

漏

Motorola, Inc. 2000

For More Information On This Product,

REV 1

1

Go to: www.freescale.com