DS2505

READ/WRITE TIMING DIAGRAM

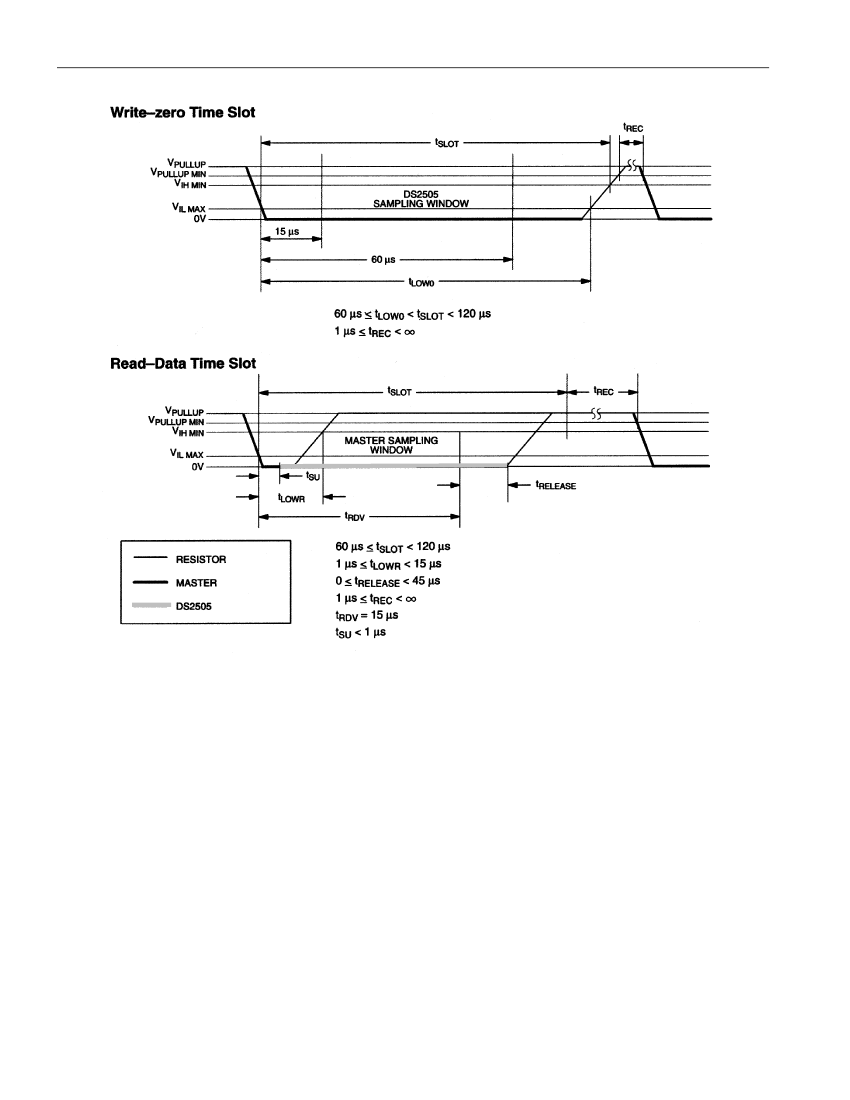

Figure 10 (cont鈥檇)

NOTE:

For read-data time slots the optimal sampling point for the master is as close as possible to the end of the

t

RDV

period without exceeding the 15 碌s window. For the case of a read-one time slot, this maximizes the

amount of time for the pull-up resistor to recover the line to a high land. For a read-zero time slot it

ensures that a read will occur before the fastest 1-Wire device releases the line (t

RELEASE

= 0).

20 of 24