鈥?/div>

2T

OSC

8T

OSC

32T

OSC

Dedicated Internal RC oscillator

For correct A/D conversions, the A/D conversion clock

(T

AD

) must be selected to ensure a minimum T

AD

time

of 1.6

碌s.

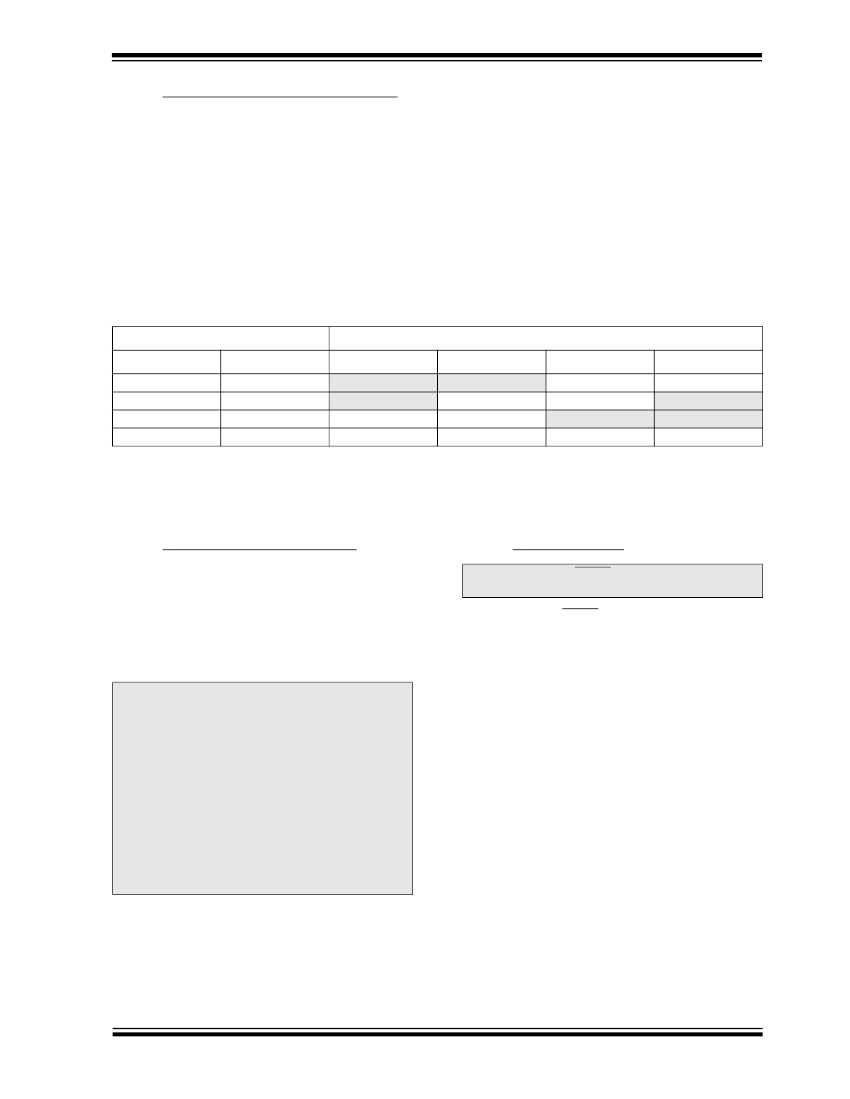

TABLE 12-1:

T

AD

vs. DEVICE OPERATING FREQUENCIES

Device Frequency

20 MHz

5 MHz

1.25 MHz

333.33 kHz

AD Clock Source (T

AD

)

Operation

2T

OSC

8T

OSC

32T

OSC

RC

Note 1:

2:

3:

4:

ADCS1:ADCS0

00

100 ns

(2)

400 ns

(2)

1.6

碌s

6

碌s

01

400 ns

(2)

1.6

碌s

6.4

碌s

24

碌s

(3)

10

1.6

碌s

6.4

碌s

25.6

碌s

(3)

96

碌s

(3)

11

2 - 6

碌s

(1,4)

2 - 6

碌s

(1,4)

2 - 6

碌s

(1,4)

2 - 6

碌s

(1)

The RC source has a typical T

AD

time of 4

碌s.

These values violate the minimum required T

AD

time.

For faster conversion times, the selection of another clock source is recommended.

For device frequencies above 1 MHz, the device must be in SLEEP for the entire conversion, or the A/D

accuracy may be out of specification.

12.3

Configuring Analog Port Pins

12.4

Note:

A/D Conversions

The GO/DONE bit should

NOT

be set in

the same instruction that turns on the A/D.

The ADCON1, TRISA and TRISE registers control the

operation of the A/D port pins. The port pins that are

desired as analog inputs must have their corresponding

TRIS bits set (input). If the TRIS bit is cleared (output),

the digital output level (V

OH

or V

OL

) will be converted.

The A/D operation is independent of the state of the

CHS<2:0> bits and the TRIS bits.

Note 1:

When reading the port register, all pins

configured as analog input channels will

read as cleared (a low level). Pins config-

ured as digital inputs will convert an ana-

log input. Analog levels on a digitally

configured input will not affect the conver-

sion accuracy.

2:

Analog levels on any pin that is defined as

a digital input, but not as an analog input,

may cause the input buffer to consume

current that is out of specification.

3:

The TRISE register is not provided on the

PIC16C745.

Clearing the GO/DONE bit during a conversion will

abort the current conversion. The ADRES register will

NOT be updated with the partially completed A/D con-

version sample. That is, the ADRES register will con-

tinue to contain the value of the last completed

conversion (or the last value written to the ADRES reg-

ister). After the A/D conversion is aborted, a 2T

AD

wait

is required before the next acquisition is started. After

this 2T

AD

wait, an acquisition is automatically started on

the selected channel.

漏

1999 Microchip Technology Inc.

Advanced Information

DS41124A-page 93