CS5510/11/12/13

2.5.1

Reading Conversions -

CS5510/12

by a new conversion word when the new conver-

sion data is available.

After power-up, the CS5510/12 will begin convert-

ing once a clock source is applied to the SCLK pin.

When a conversion has completed, and there is

new data in the output register, the SDO line will

fall to a logic-low level if CS is also at a logic-low

state (SDO will always be high-impedance when

CS is high). If CS is low at the end of the conver-

sion cycle, SDO will fall on the rising edge of an

SCLK. After SCLK falls, the next SCLK cycle (high,

then low) will begin clocking out the data. The first

data bit therefore, is 1-

锟?frac12;

SCLK cycles wide. Twen-

ty-four SCLK cycles (after the initial high-low tran-

sition) are needed to retrieve the conversion word

from the device (see Figures 16 and 17). The data

bits can be read on the rising edge of SCLK, and

the next data bit is output to SDO on the falling

edge of SCLK. Once the entire data word has been

read, SDO will return to a logic-high state until

there is a new conversion word available. If CS is

at a logic-high at the end of the conversion cycle,

the data will not be shifted out of the part until CS

is brought to a logic-low state during the next con-

version cycle. If a new conversion becomes avail-

able while the current data is being read, the data

register will not be updated, and the new conver-

sion word will be lost. The user need not read every

conversion. If the user chooses not to read a con-

version, CS should remain at a logic-high state for

the duration of the conversion cycle. Note that if

CS goes to a logic-high state during a read, the

current conversion data will be lost and replaced

2.5.2

Reading Conversions -

CS5511/13

After power-up, the CS5511/13 begins converting

and updating the output register. When there is

new data in the output register (at the end of a con-

version cycle) the SDO line will fall to a logic-low

level if CS is also at a logic-low state (SDO will al-

ways be high-impedance when CS is high). Twen-

ty-four SCLK cycles are needed to retrieve the

conversion word from the device (see Figures 18

and 19). The data bits can be read on the rising

edge of SCLK, and the next data bit is output to

SDO on the falling edge of SCLK. Once the entire

data word has been read, SDO will return to a log-

ic-high state until there is a new conversion word

available. If new conversions become available

while the current data is being read, the data regis-

ter will not be updated, and the new conversions

will be lost. The user need not read every conver-

sion. If the user chooses not to read a conversion

after SDO falls, SDO will rise seventeen oscillator

clock cycles (of the internal oscillator) before the

next conversion word is available and then fall

again to signal that the conversion is complete.

Note that if a conversion word is not read before

the next conversion word is ready, or if CS goes to

a logic-high state during a read, the current conver-

sion data will be lost and replaced by a new con-

version word when the new conversion data is

available.

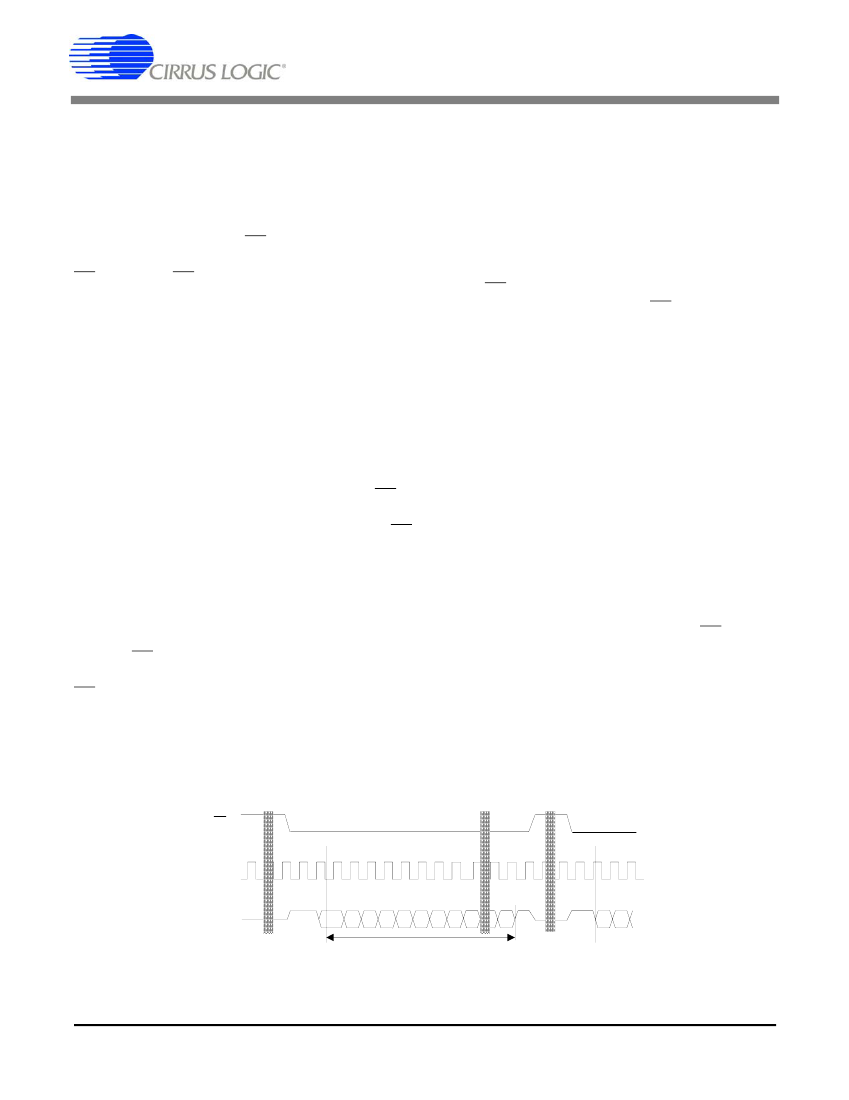

CS

SC LK

SDO

0

OF

OD

0

0

0

0

0

M SB

LSB

0

0

D a ta T im e

24 SC LKs

Figure 16. Data Word Timing for the CS5510.

16

DS337F3