所选 PLL 合成器 IC 的选择允许将相对采样时钟相位调整注入到每个数字化器 IC 中。通过创建反馈机制来补偿热漂移以及由此产生的每个 IC 的采样时钟和 SYSREF 之间的 PLL 相位漂移,确保每个数字化仪 IC 的第一个传输...

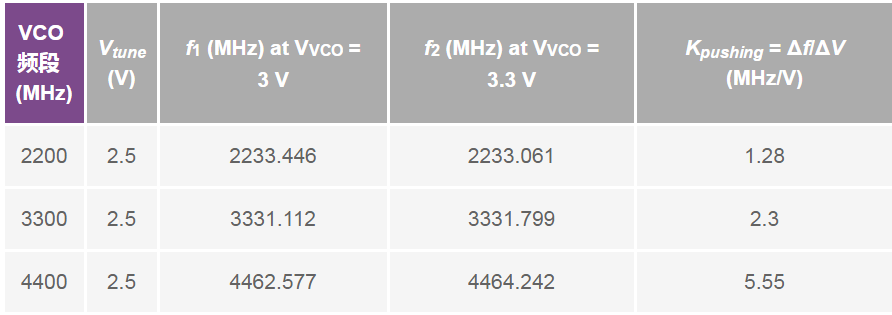

将受控振荡器所需的频率调谐范围分成离散频带是一种常用技术。拥有多个频段的优势在于可以覆盖较宽的调谐范围,同时在每个频段内保持相对较低的压控振荡器 (VCO) 增益。低 VCO 增益有利于实现低 VCO 相位噪声。要求...

您经常需要屏蔽特定频率的信号;在这些频率中,50 或 60 赫兹的线路频率是最常见的。您可以使用图 1中的 PLL 陷波滤波器 来阻止不需要的频率。IC 1是一个 LM567C,是一个音调解码器。组件 C 1、R 1A和 R 1B 决定了 I...

时间:2023-03-25 阅读:196 关键词:PLL 滤波器

在这篇产品操作方法文章中,IDT 的 Fred Hirning 描述了在处理基于 FPGA 的高速通信接口(例如 SerDes)中的时钟抖动时所面临的问题,以及外部锁相环 (PLL)(例如公司的 VersaClock5)如何处理FemtoClock NG时钟发生...

时间:2023-03-14 阅读:249 关键词: FPGA 通信接口

锁相环(PLL)是现代通信系统的基本构建模块PLLs 通常用在无线电接收机或发射机中,主要提供"本振"(LO)功能;也可用于时钟信号分配和降噪,而且越来越多地用作高采...

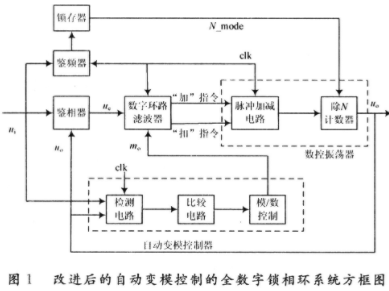

目前数字锁相环在数字通信、雷达、无线电电子学、仪表仪器、高速计算机及导航系统中得到了广泛的应用。与传统的模拟锁相环相比,全数字锁相环克服了模拟锁相环易受电压变化...

分类:元器件应用 时间:2020-08-12 阅读:402

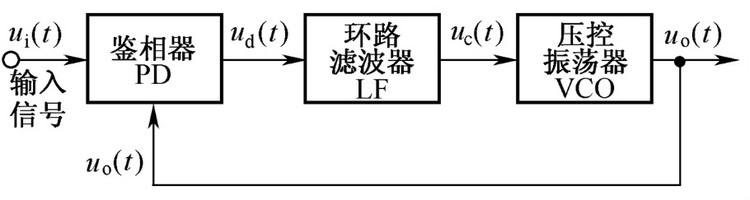

因锁相环可以实现输出信号频率对输入信号频率的自动跟踪,所以锁相环通常用于闭环跟踪电路。锁相环在工作的过程中,当输出信号的频率与输入信号的频率相等时,输出电压与输入电压保持固定的相位差值,即输出电压与输...

时间:2020-03-17 阅读:698

在以太网中,物理层芯片(Physical Layer Interface Devices,PHY)是将各网元连接到物理介质上的关键部件。负责完成互连参考模型(OSI)第I层中的功能,即为链路层实体之...

时间:2019-10-17 阅读:786 关键词:芯片,PLL

对于数字波束成形相控阵,要生成本地振荡器(LO) ,通常会考虑的实现方法是向分布于天线阵列中的一系列锁相环分配常用基准频率。对于这些分布式锁相环,目前文献中还没有...

分类:其它 时间:2019-04-17 阅读:1629

锁相环是最通用的电路功能之一。它们用于为处理器提供时钟(相当良好的情况),以及用于在固定和调谐频率发送器和接收器中建立调谐。 然而,最困难的挑战之一是在无线链路中恢复,清理和重新计时定时信号。与处理器...

锁相的意义是相位同步的自动控制,能够完成两个电信号相位同步的自动控制闭环系统叫做锁相环,简称PLL。它广泛应用于广播通信、频率合成、自动控制及时钟同步等技术领域。...

分类:元器件应用 时间:2018-10-31 阅读:14035

ADI针对下一代射频、微波和毫米波应用推出PLL/VCO解决方案

中国,北京—Analog Devices, Inc. (ADI)近日宣布推出一款先进的频率合成器ADF4371,采用了锁相环(PLL)、完全集成式压控振荡器(VCO)并集成低压差调节器(LDO)和跟踪滤波器技...

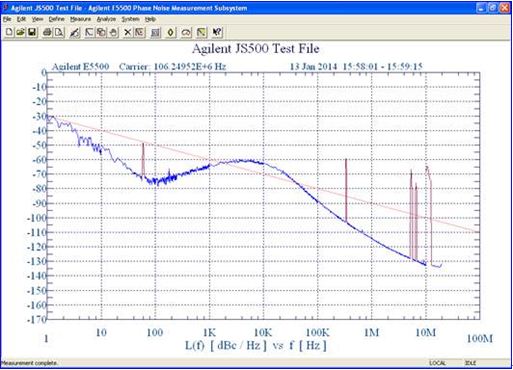

也许你也会跟我一样认为典型数据表中的某些规格难以理解,这是因为其中涵盖了一些你不太熟悉的隐含惯例。对许多RF系统工程师而言,其中一种规格便是锁相环(PLL)中的相位噪...

分类:其它 时间:2017-05-09 阅读:1068

简介 设计并调试锁相环(PLL)电路可能会很复杂,除非工程师深入了解PLL理论以及逻辑开发过程。本文介绍PLL设计的简易方法,并提供有效、符合逻辑的方法调试PLL问题。 ...

时间:2017-03-10 阅读:2066

假设您已经通过迭代信息传递相位边限和回路带宽在锁相环(PLL)上花费了一些时间。但遗憾地是,还是无法在相位噪声、杂散和锁定时间之间达成良好的平衡。感到泄气?想要放...

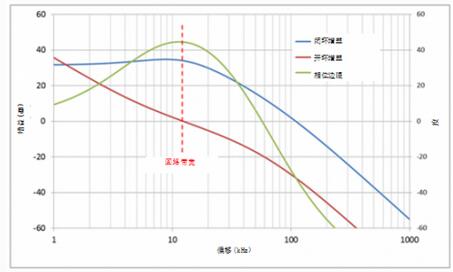

电路功能与优势 图1所示PLL电路采用13 GHz小数N分频频率合成器、宽带有源环路滤波器和VCO,5°以内的200 MHz跳频相位建立时间短于5 µs。 采用带宽为2.4 MHz的有源环路滤波器获得该性能。由于ADF4159...

分类:其它 时间:2016-07-21 阅读:1094

我们可能都见到过需要随时间变化扫描频率的情况。如果您遇到这样的问题,可以考虑雷达等应用,在这类应用中发送的信号不仅可由目标反射回来,而且还能够与接收到的信号进行...

分类:模拟技术 时间:2014-08-26 阅读:1426

导读:对于性能密集型应用(例如FPGA和以太网PHY时钟)来说,评估和选择合适的基于PLL的振荡器以最小化相位噪声和抖动峰值是必要的。 十几年前,频率控制行业推出了基...

凌力尔特推出集成型VCO的高性能分数N PLL LTC6948

导读:凌力尔特公司 (Linear Technology Corporation) 推出一款具 6GHz+ 集成型 VCO 的高性能分数 N PLL LTC6948。在 LTC6948 的是一个四阶 ΔΣ 调制器,其运用智能噪声整形技术以限度地抑制噪声成分,并且不会产生...