鈭?/div>

10碌s

WDO CONNECTED TO

碌P

INTERRUPT

RESET PULLED UP TO V

CC

RESET

t

RP

t

WP

t

RP

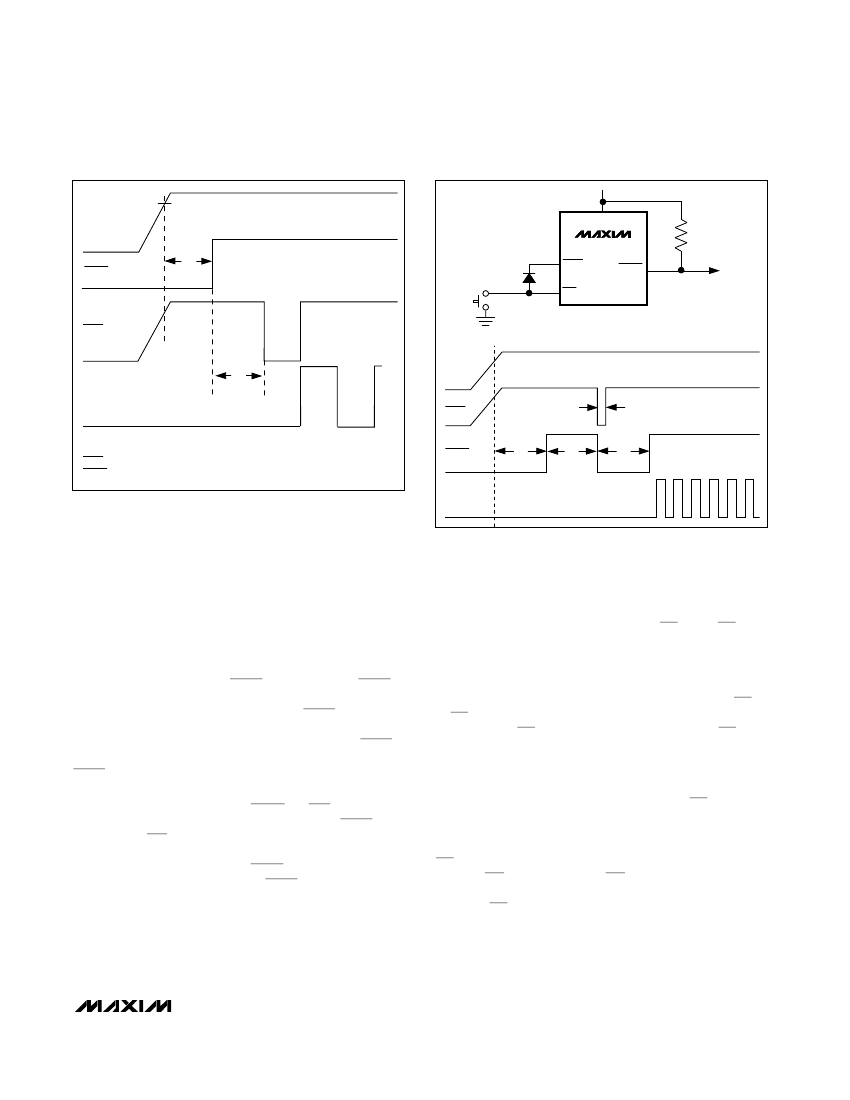

Figure 5. Watchdog Timing Relationship

WDI

either when a reset occurs or when a transition (low-to-

high or high-to-low) takes place at WDI. As long as

reset is asserted, the timer remains cleared and does

not count. As soon as reset is released or WDI

changes state, the timer starts counting (Figure 5).

WDI can detect pulses as short as 100ns. Unlike the

5V MAX690 family, the watchdog function

cannot

be

disabled.

Figure 6. Generating a Reset on Each Watchdog Fault

Chip-Enable Signal Gating

Internal gating of chip-enable (CE) signals prevents erro-

neous data from corrupting CMOS RAM in the event of an

undervoltage condition. The MAX793/MAX794/MAX795

use a series transmission gate from CE IN to CE OUT

(Figure 7). During normal operation (reset not asserted),

the CE transmission gate is enabled and passes all CE

transitions. When reset is asserted, this path becomes

disabled, preventing erroneous data from corrupting the

CMOS RAM. The short CE propagation delay from CE IN

to CE OUT enables these 碌P supervisors to be used with

most 碌Ps. If CE IN is low when reset asserts, CE OUT

remains low for typically 10碌s to permit completion of the

current write cycle.

Watchdog Output (MAX793/MAX794)

In the MAX793/MAX794, WDO remains high (WDO is

pulled up to V

CC

) if there is a transition or pulse at WDI

during the watchdog timeout period. WDO goes low if

no transition occurs at WDI during the watchdog timeout

period. The watchdog function is disabled and WDO is

a logic high when reset is asserted if V

CC

is above V

SW

.

WDO is a logic low when V

CC

is below V

SW

.

If a system reset is desired on every watchdog fault,

simply diode-OR connect WDO to MR (Figure 6).

When a watchdog fault occurs in this mode, WDO goes

low, pulling MR low, which causes a reset pulse to be

issued. Ten microseconds after reset is asserted, the

watchdog timer clears and WDO returns high. This

delay results in a 10碌s pulse at WDO, allowing external

circuitry to 鈥渃apture鈥?a watchdog fault indication. A

continuous high or low on WDI will cause 200ms reset

pulses to be issued every 1.6sec.

Chip-Enable Input

The CE transmission gate is disabled and CE IN is high

impedance (disabled mode) while reset is asserted.

During a power-down sequence when V

CC

passes the

reset threshold, the CE transmission gate disables and

CE IN immediately becomes high impedance if the volt-

age at CE IN is high. If CE IN is low when reset

asserts, the CE transmission gate will disable at the

moment CE IN goes high, or 10碌s after reset asserts,

whichever occurs first (Figure 8). This permits the cur-

rent write cycle to complete during power-down.

______________________________________________________________________________________

11