鈥?/div>

Embedded MPC8xx core up to 133 MHz

Maximum frequency operation of the external bus is 80 MHz (in 1:1 mode)

鈥?The 133-MHz core frequency supports 2:1 mode only.

鈥?The 66-/80-MHz core frequencies support both the 1:1 and 2:1 modes.

Single-issue, 32-bit core (compatible with the PowerPC architecture definition) with thirty-two 32-bit

general-purpose registers (GPRs)

鈥?The core performs branch prediction with conditional prefetch and without conditional execution.

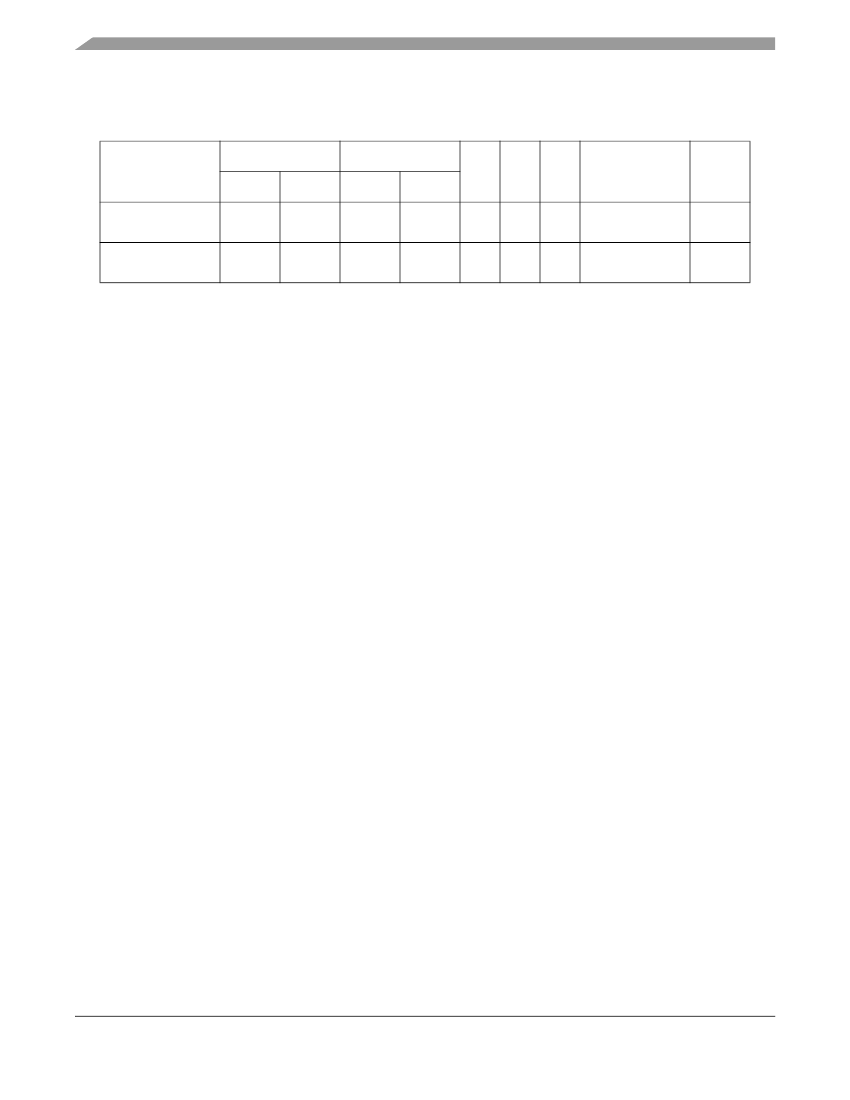

鈥?8-Kbyte data cache and 8-Kbyte instruction cache (see

Table 1)

鈥?Instruction cache is two-way, set-associative with 256 sets in 2 blocks

鈥?Data cache is two-way, set-associative with 256 sets

鈥?Cache coherency for both instruction and data caches is maintained on 128-bit (4-word) cache

blocks.

鈥?Caches are physically addressed, implement a least recently used (LRU) replacement algorithm, and

are lockable on a cache block basis.

鈥?MMUs with 32-entry TLB, fully associative instruction and data TLBs

鈥?MMUs support multiple page sizes of 4, 16, and 512 Kbytes, and 8 Mbytes; 16 virtual address spaces

and 16 protection groups

鈥?Advanced on-chip emulation debug mode

Provides enhanced ATM functionality found on the MPC862 and MPC866 families and includes the

following:

鈥?Improved operation, administration and maintenance (OAM) support

鈥?OAM performance monitoring (PM) support

鈥?Multiple APC priority levels available to support a range of traffic pace requirements

鈥?Port-to-port switching capability without the need for RAM-based microcode

鈥?Simultaneous MII (100BaseT) and UTOPIA (half- or full -duplex) capability

鈥?Optional statistical cell counters per PHY

鈥?/div>

鈥?/div>

MPC885/MPC880 Hardware Specifications, Rev. 3

2

Freescale Semiconductor