鈥?/div>

Unit

ns

ns

MII_RX_CLK period

MII_RX_CLK period

ns

ns

M1_RMII RMII_RXD[1:0], RMII_CRS_DV, RMII_RX_ERR to RMII_REFCLK

setup

M2_RMII RMII_REFCLK to RMII_RXD[1:0], RMII_CRS_DV, RMII_RX_ERR

hold

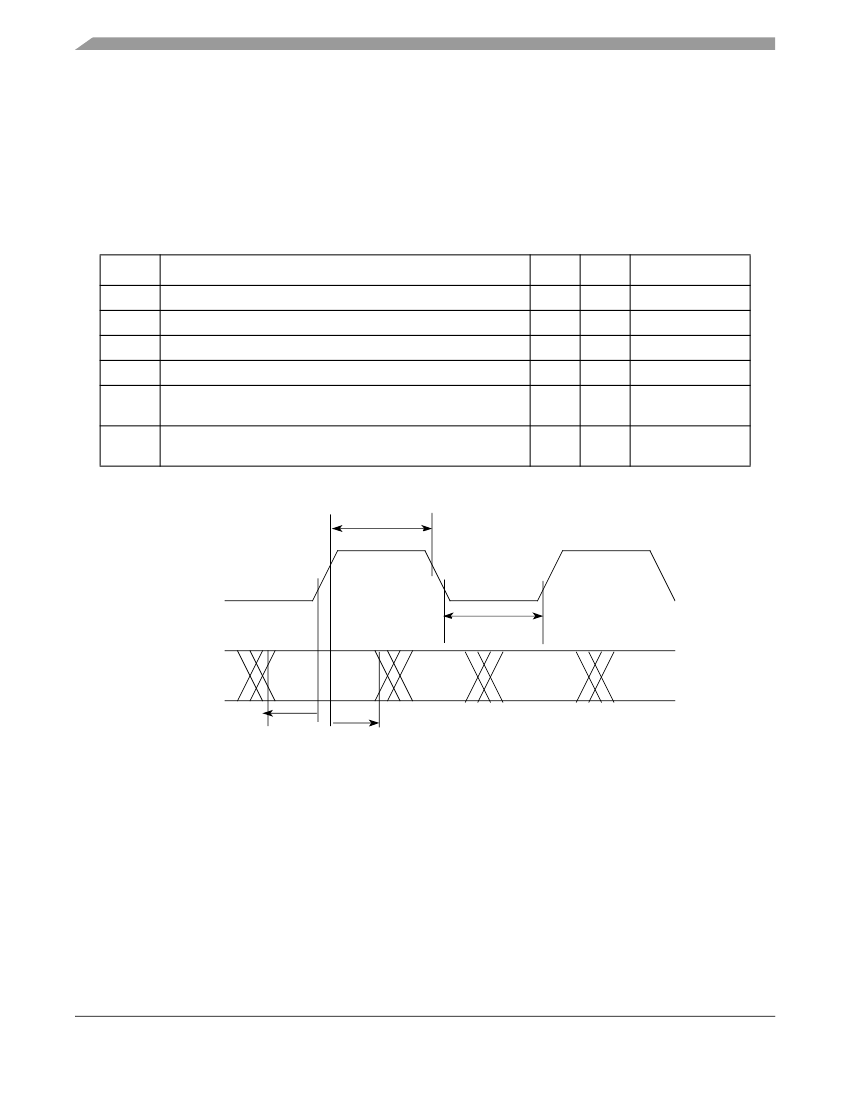

Figure 72

shows MII receive signal timing.

M3

MII_RX_CLK (input)

M4

MII_RXD[3:0] (inputs)

MII_RX_DV

MII_RX_ER

M1

M2

Figure 72. MII Receive Signal Timing Diagram

15.2 MII and Reduced MII Transmit Signal Timing

The transmitter functions correctly up to a MII_TX_CLK maximum frequency of 25 MHz +1%. The RMII

transmitter functions correctly up to a RMII_REFCLK maximum frequency of 50 MHz +1%. There is no minimum

frequency requirement. In addition, the processor clock frequency must exceed the MII_TX_CLK frequency

鈥?/div>

1%.

MPC885/MPC880 Hardware Specifications, Rev. 3

72

Freescale Semiconductor