PIC16C717/770/771

EXAMPLE 3-1:

BCF

CLRF

INITIALIZING PORTA

;

;

;

;

;

;

;

;

;

;

;

Select Bank 0

Initialize PORTA by

clearing output

data latches

Select Bank 1

Value used to

initialize data

direction

Set RA<3:0> as inputs

RA<7:4> as outputs. RA<7:6>availability depends on oscillator selection.

Set RA<1:0> as analog inputs, RA<7:2> are digital I/O

STATUS, RP0

PORTA

BSF

MOVLW

STATUS, RP0

0Fh

MOVWF

MOVLW

MOVWF

BCF

TRISA

03

ANSEL

STATUS, RP0

; Return to Bank 0

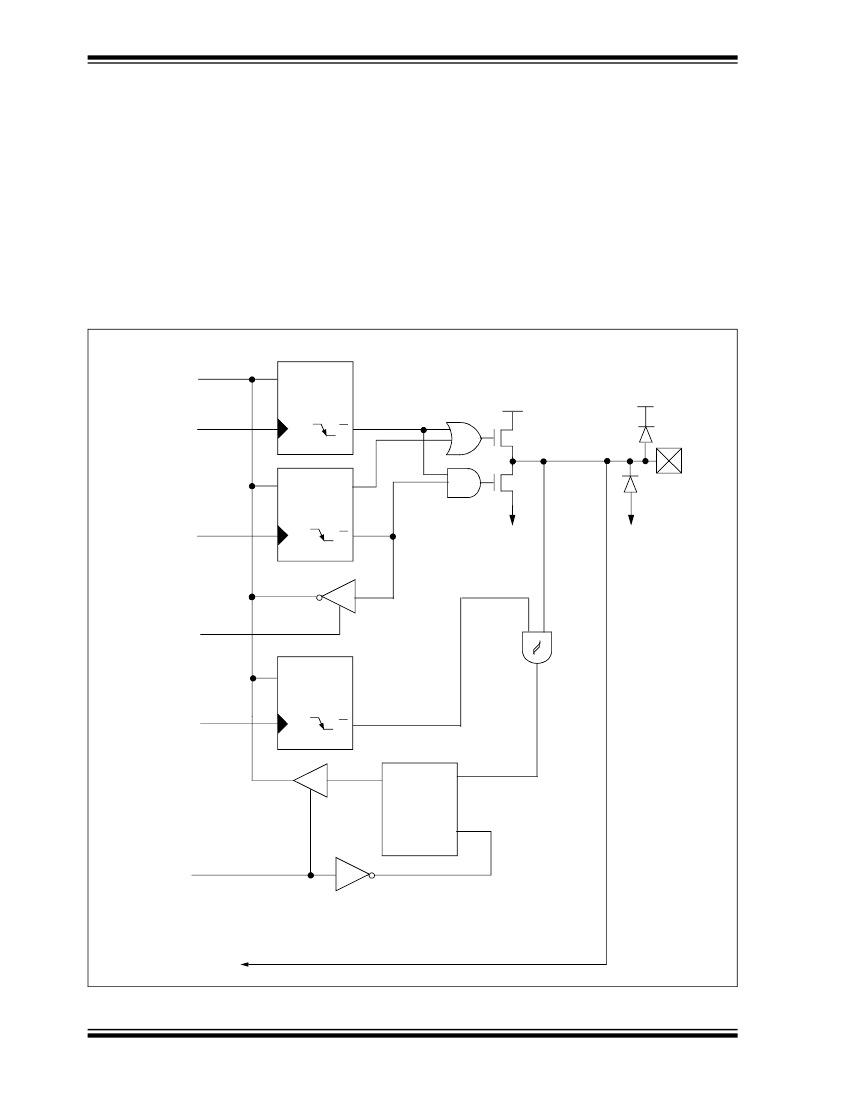

FIGURE 3-1:

BLOCK DIAGRAM OF RA0/AN0, RA1/AN1/LVDIN

Data

Bus

Data Latch

D

Q

V

DD

CK

Q

P

V

DD

WR

PORT

TRIS Mode

D

WR

TRIS

Q

N

CK

Q

V

SS

V

SS

RD

TRIS

Analog Select

D

WR

ANSEL

CK

Q

Q

Schmitt

Trigger

Q

D

EN

RD

PORT

To A/D Converter input or LVD Module input

DS41120A-page 28

Advanced Information

漏

1999 Microchip Technology Inc.