PIC16C717/770/771

i)

The MSSP Module shifts in the ACK bit from the

slave device and writes its value into the

SSPCON2 register ( SSPCON2<6>).

The MSSP module generates an interrupt at the

end of the ninth clock cycle by setting the SSPIF

bit.

The user generates a STOP condition by setting

the STOP enable bit PEN in SSPCON2.

Interrupt is generated once the STOP condition

is complete.

BAUD RATE GENERATOR

In I

2

C master mode, the BRG is reloaded automatically.

If Clock Arbitration is taking place for instance, the BRG

will be reloaded when the SCL pin is sampled high

(Figure

9-16).

j)

k)

l)

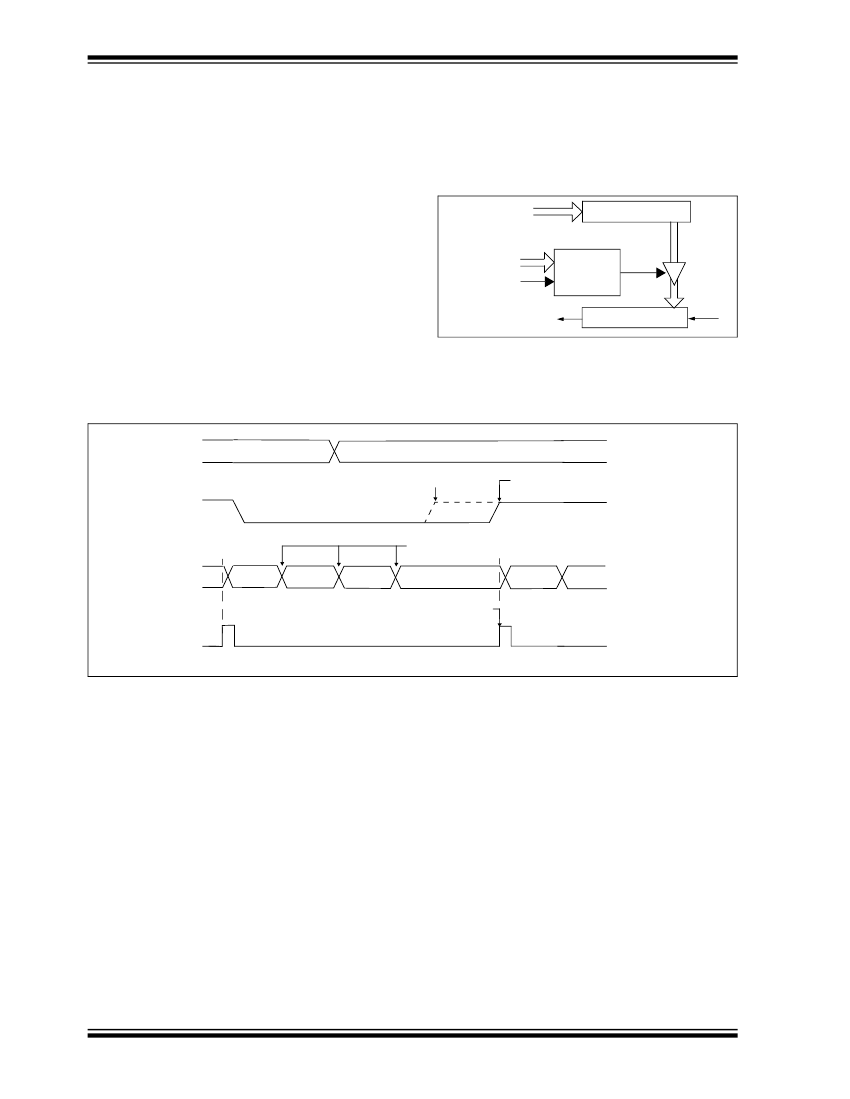

FIGURE 9-15: BAUD RATE GENERATOR

BLOCK DIAGRAM

SSPM<3:0>

SSPADD<6:0>

9.2.8

SSPM<3:0>

SCL

CLKOUT

Reload

Control

Reload

In I

2

C master mode, the reload value for the BRG is

located in the lower 7 bits of the SSPADD register

(Figure

9-15).

When the BRG is loaded with this value,

the BRG counts down to 0 and stops until another

reload has taken place. The BRG count is decremented

twice per instruction cycle (T

CY

) on the Q2 and Q4

clock.

BRG Down Counter

F

OSC

/4

FIGURE 9-16: BAUD RATE GENERATOR TIMING WITH CLOCK ARBITRATION

SDA

DX

DX-1

SCL allowed to transition high

SCL de-asserted but slave holds

SCL low (clock arbitration)

SCL

BRG decrements

(on Q2 and Q4 cycles)

BRG

value

03h

02h

01h

00h (hold off)

03h

02h

SCL is sampled high, reload takes

place, and BRG starts its count.

BRG

reload

DS41120A-page 86

Advanced Information

漏

1999 Microchip Technology Inc.