PIC16C717/770/771

6.1.1

TIMER1 COUNTER OPERATION

In this mode, Timer1 is being incremented via an exter-

nal source. Increments occur on a rising edge. After

Timer1 is enabled in counter mode, the module must

first have a falling edge before the counter begins to

increment.

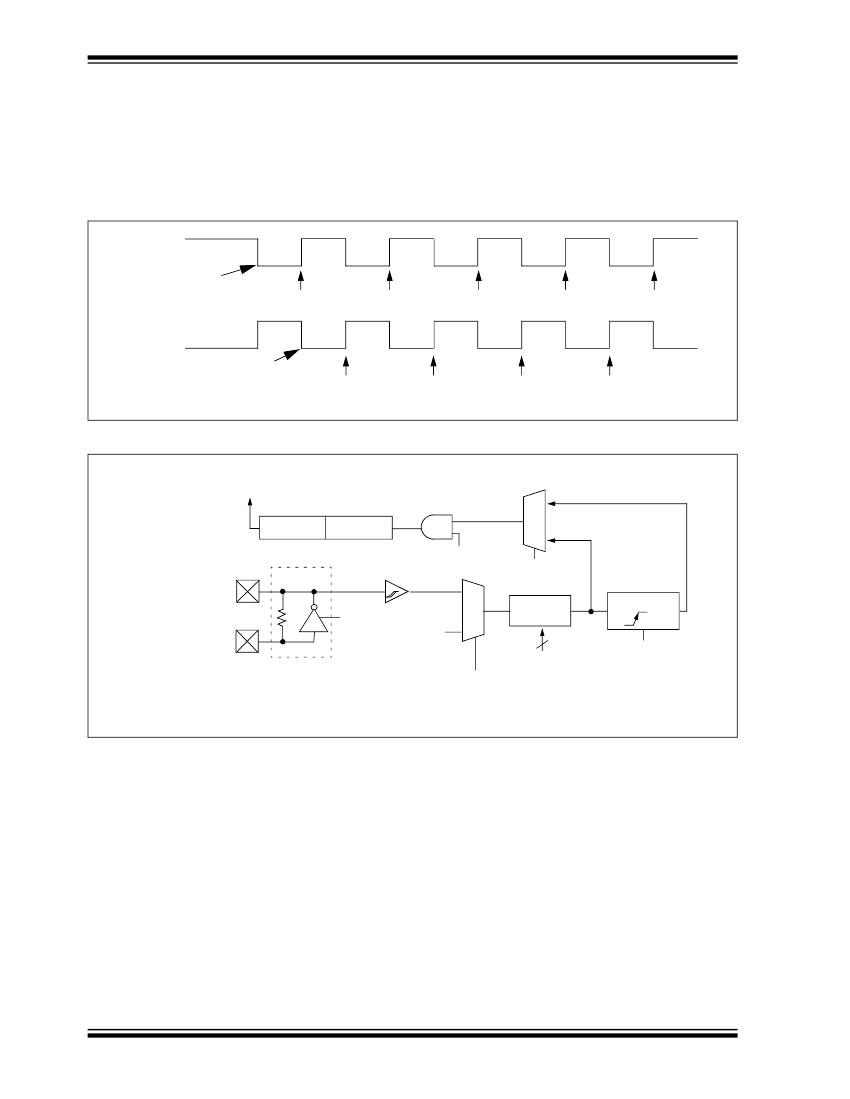

FIGURE 6-1:

T1CKI

(Initially high)

TIMER1 INCREMENTING EDGE

First falling edge

of the T1ON enabled

T1CKI

(Initially low)

First falling edge

of the T1ON enabled

Note:

Arrows indicate counter increments.

FIGURE 6-2:

TIMER1 BLOCK DIAGRAM

Set flag bit

TMR1IF on

Overflow

TMR1H

TMR1

TMR1L

0

1

TMR1ON

on/off

T1SYNC

Synchronized

clock input

T1OSC

RB6/T1OSO/T1CKI/P1C

T1OSCEN F

OSC

/4

Enable

Internal

Oscillator

(1)

Clock

1

Prescaler

1, 2, 4, 8

0

2

T1CKPS<1:0>

TMR1CS

SLEEP input

Synchronize

det

RB7/T1OSI/P1D

Note 1:

When the T1OSCEN bit is cleared, the inverter and feedback resistor are turned off. This eliminates power drain.

DS41120A-page 50

Advanced Information

漏

1999 Microchip Technology Inc.