PIC16C717/770/771

8.3.5

PROGRAMMABLE DEADBAND DELAY

In half-bridge or full-bridge applications, where all

power switches are modulated at the PWM frequency

at all time, the power switches normally require longer

time to turn off than to turn on. If both the upper and

lower power switches are switched at the same time

(one turned on, and the other turned off), both switches

will be on for a short period of time, until one switch

completely turns off. During this time, a very high cur-

rent, called shoot-through current, will flow through

both power switches, shorting the bridge supply. To

avoid this potentially destructive shoot-through current

from flowing during switching, turning on the power

switch is normally delayed to allow the other switch to

completely turn off.

In the Half-Bridge Output mode, a digitally program-

mable deadband delay is available to avoid shoot-

through current from destroying the bridge power

switches. The delay occurs at the signal transition from

the non-active state to the active state. See

Figure 8-6

for illustration. The P1DEL register sets the amount of

delay.

REGISTER 8-2:

R/W-0

bit7

R/W-0

PWM DELAY REGISTER (P1DEL: 97H)

R/W-0

R/W-0

R/W-0

R/W-0

R/W-0

R/W-0

bit0

R = Readable bit

W = Writable bit

U = Unimplemented bit, read as

鈥?鈥?/div>

- n = Value at POR reset

bit 7-0:

P1DEL<7:0>: PWM Delay count for Half-Bridge output mode:

Number of F

OSC

/4 (Tosc

鈥?/div>

4) cycles

between the P1A transition and the P1B transition.

8.3.6

DIRECTION CHANGE IN FULL-BRIDGE

OUTPUT MODE

In the Full-Bridge Output mode, the PWM1M1 bit in the

CCP1CON register allows user to control the Forward/

Reverse direction. When the application firmware

changes this direction control bit, the ECCP module will

assume the new direction on the next PWM cycle. The

current PWM cycle still continues, however, the non-

modulated outputs, P1A and P1C signals, will transition

to the new direction TOSC, 4

鈥?/div>

TOSC or 16

鈥?/div>

TOSC (for

Timer2 presale T2CKRS<1:0> = 00, 01 and 1x respec-

tively) earlier, before the end of the period. During this

transition cycle, the modulated outputs, P1B and P1D,

will go to the inactive state. See

Figure 8-10

for illustra-

tion.

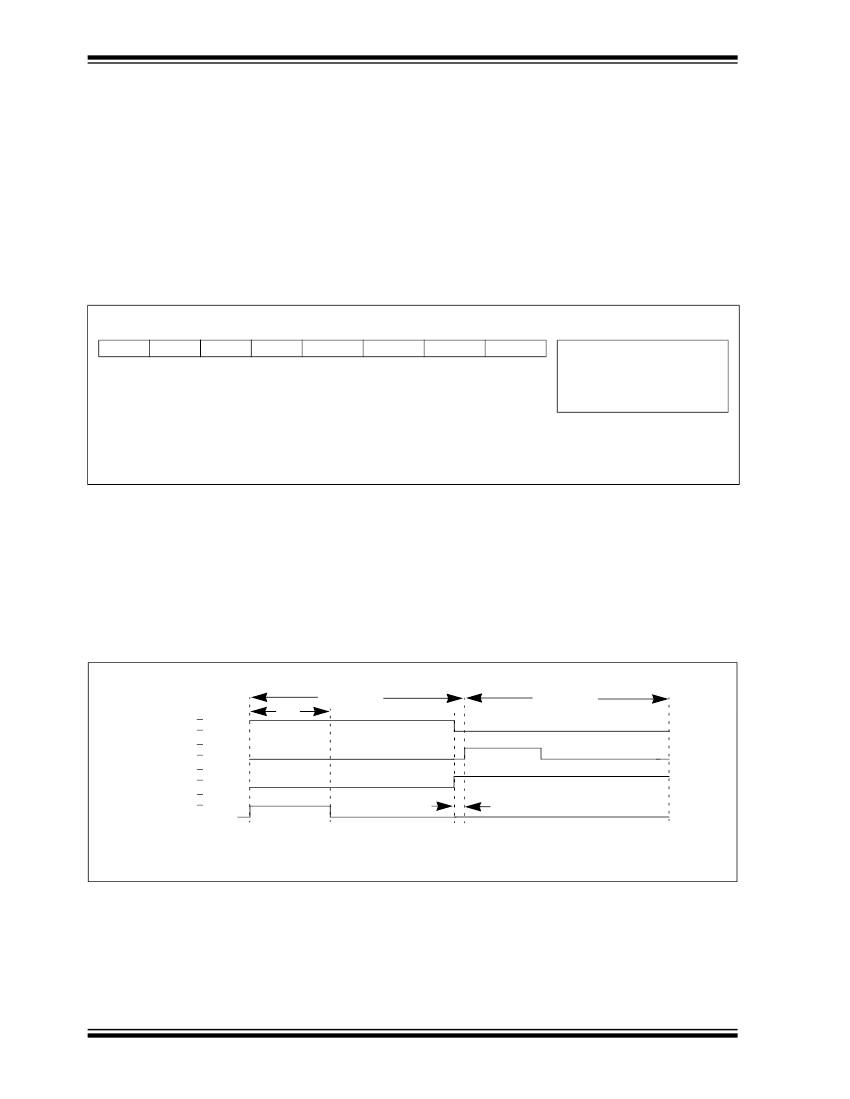

FIGURE 8-10: PWM DIRECTION CHANGE

(1)

SIGNAL

P1A (Active High)

P1B (Active High)

P1C (Active High)

P1D (Active High)

Note 1:

2:

(2)

PERIOD

DC

PERIOD

The Direction bit in the ECCP Control Register (CCP1CON.PWM1M1) is written anytime during the PWM cycle.

The P1A and P1C signals switch T

OSC

, 4*Tosc or 16*T

OSC

depending on the Timer2 prescaler value earlier when

changing direction. The modulated P1B and P1D signals are inactive at this time.

DS41120A-page 64

Advanced Information

漏

1999 Microchip Technology Inc.