PIC16F87X

4.3

Reading the Data EEPROM Memory

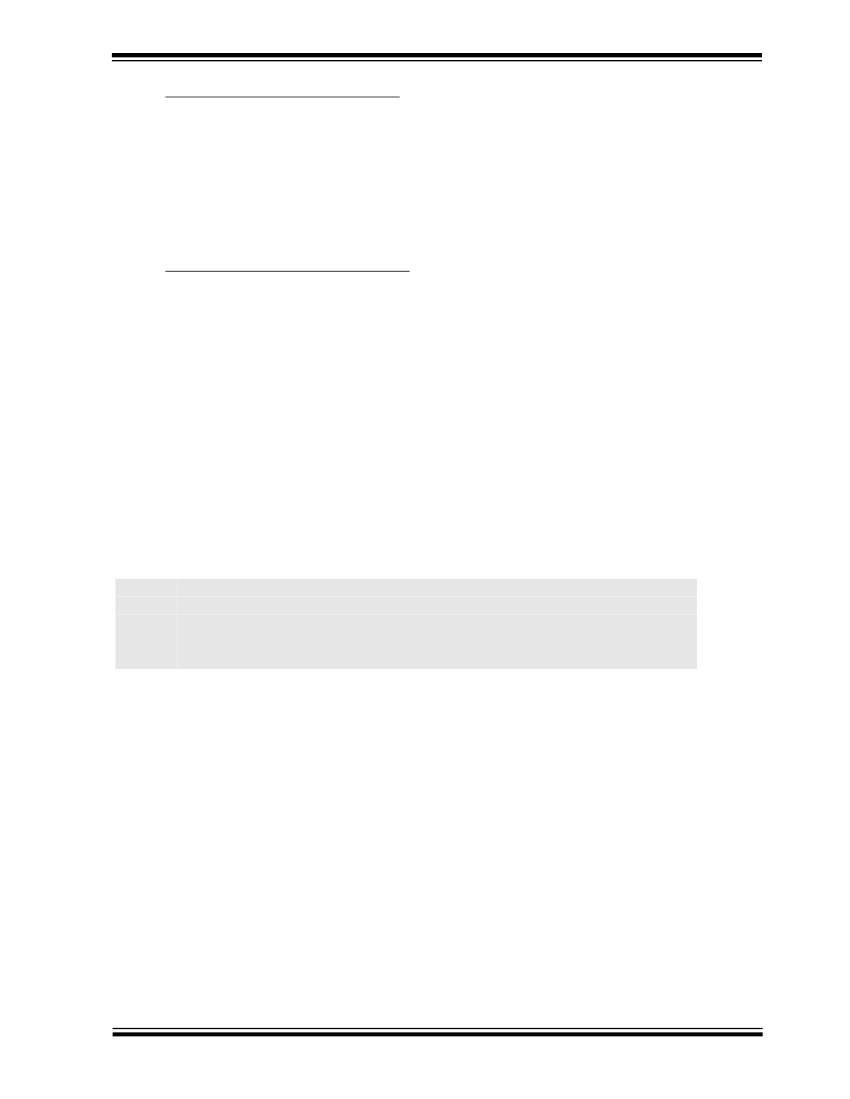

EXAMPLE 4-1:

BSF

BCF

MOVLW

MOVWF

BSF

BCF

BSF

BCF

MOVF

To read a data memory location, the user must write the

address to the EEADR register, clear the EEPGD con-

trol bit (EECON1<7>) and then set control bit RD

(EECON1<0>). The data is available in the very next

instruction cycle of the EEDATA register, therefore it

can be read by the next instruction. EEDATA will hold

this value until another read operation or until it is writ-

ten to by the user (during a write operation).

DATA EEPROM READ

STATUS, RP1 ;

STATUS, RP0 ;Bank 2

DATA_EE_ADDR ;

EEADR

;Data Memory Address to read

STATUS, RP0 ;Bank 3

EECON1, EEPGD ;Point to DATA memory

EECON1, RD

;EEPROM Read

STATUS, RP0 ;Bank 2

EEDATA, W

;W = EEDATA

4.4

Writing to the Data EEPROM Memory

To write an EEPROM data location, the address must

first be written to the EEADR register and the data writ-

ten to the EEDATA register. Then the sequence in

Example 4-2 must be followed to initiate the write cycle.

EXAMPLE 4-2:

DATA EEPROM WRITE

BSF

BCF

MOVLW

MOVWF

MOVLW

MOVWF

BSF

BCF

BSF

STATUS, RP1

STATUS, RP0

DATA_EE_ADDR

EEADR

DATA_EE_DATA

EEDATA

STATUS, RP0

;

; Bank 2

;

; Data Memory Address to write

;

; Data Memory Value to write

; Bank 3

EECON1, EEPGD ; Point to DATA memory

EECON1, WREN

; Enable writes

BCF

MOVLW

Required

Sequence

MOVWF

MOVLW

MOVWF

BSF

BSF

SLEEP

BCF

INTCON, GIE

55h

EECON2

AAh

EECON2

EECON1, WR

INTCON, GIE

; Disable Interrupts

;

; Write 55h

;

; Write AAh

; Set WR bit to begin write

; Enable Interrupts

; Wait for interrupt to signal write complete

EECON1, WREN

; Disable writes

The write will not initiate if the above sequence is not

exactly followed (write 55h to EECON2, write AAh to

EECON2, then set WR bit) for each byte. It is strongly

recommended that interrupts be disabled during this

code segment.

Additionally, the WREN bit in EECON1 must be set to

enable writes. This mechanism prevents accidental

writes to data EEPROM due to unexpected code exe-

cution (i.e., runaway programs). The WREN bit should

be kept clear at all times, except when updating the

EEPROM. The WREN bit is not cleared by hardware

After a write sequence has been initiated, clearing the

WREN bit will not affect the current write cycle. The WR

bit will be inhibited from being set unless the WREN bit

is set. The WREN bit must be set on a previous instruc-

tion. Both WR and WREN cannot be set with the same

instruction.

At the completion of the write cycle, the WR bit is

cleared in hardware and the EEPROM Write Complete

Interrupt Flag bit (EEIF) is set. EEIF must be cleared by

software.

漏

1999 Microchip Technology Inc.

DS30292B-page 43