PIC16F87X

9.2.14

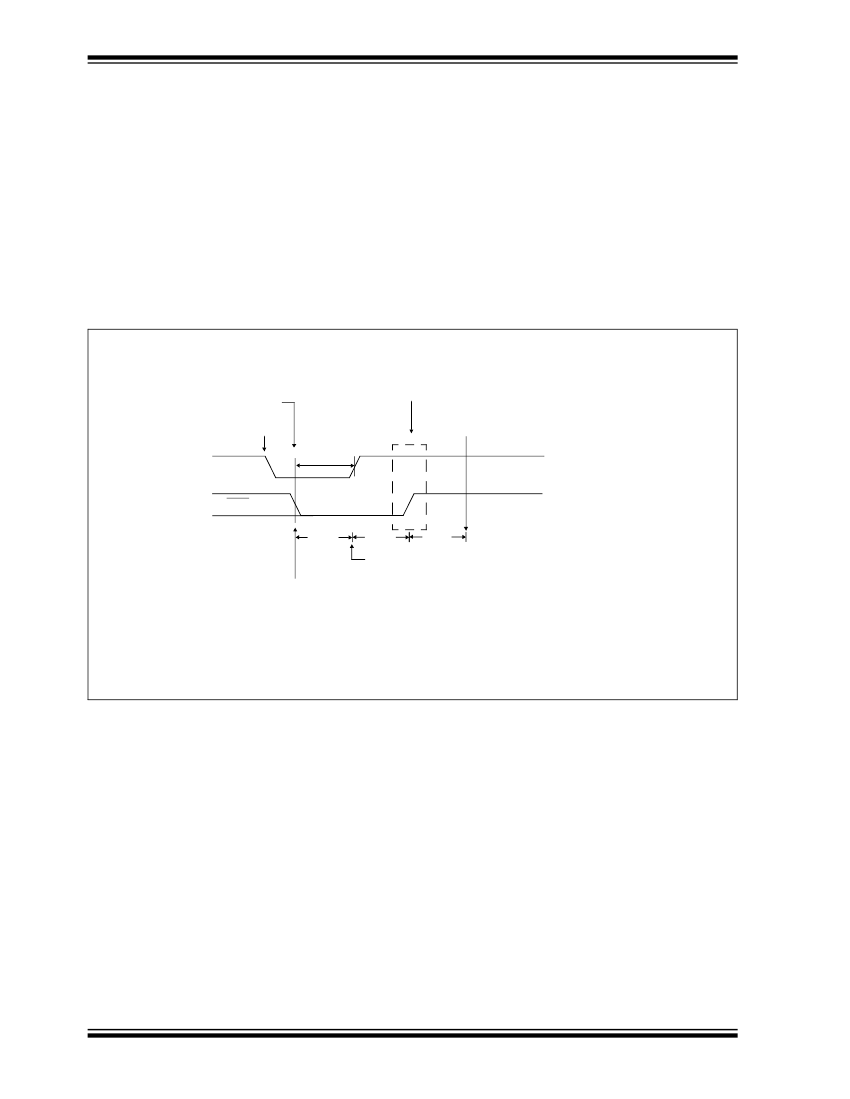

STOP CONDITION TIMING

A stop bit is asserted on the SDA pin at the end of a

receive/transmit by setting the Stop Sequence Enable

bit PEN (SSPCON2<2>). At the end of a receive/trans-

mit, the SCL line is held low after the falling edge of the

ninth clock. When the PEN bit is set, the master will

assert the SDA line low . When the SDA line is sam-

pled low, the baud rate generator is reloaded and

counts down to 0. When the baud rate generator times

out, the SCL pin will be brought high, and one T

BRG

(baud rate generator rollover count) later, the SDA pin

will be deasserted. When the SDA pin is sampled high

while SCL is high, the P bit (SSPSTAT<4>) is set. A

T

BRG

later, the PEN bit is cleared and the SSPIF bit is

set (Figure

9-17).

Whenever the firmware decides to take control of the

bus, it will first determine if the bus is busy by checking

the S and P bits in the SSPSTAT register. If the bus is

busy, then the CPU can be interrupted (notified) when

a Stop bit is detected (i.e. bus is free).

9.2.14.1

WCOL STATUS FLAG

If the user writes the SSPBUF when a STOP sequence

is in progress, then WCOL is set and the contents of the

buffer are unchanged (the write doesn鈥檛 occur).

FIGURE 9-17: STOP CONDITION RECEIVE OR TRANSMIT MODE

Write to SSPCON2

Set PEN

Falling edge of

9th clock

T

BRG

SCL

SCL = 1 for T

BRG

, followed by SDA = 1 for T

BRG

after SDA sampled high. P bit (SSPSTAT<4>) is set

PEN bit (SSPCON2<2>) is cleared by

hardware and the SSPIF bit is set

SDA

ACK

P

T

BRG

T

BRG

T

BRG

SCL brought high after T

BRG

SDA asserted low before rising edge of clock

to setup stop condition.

Note:

T

BRG

= one baud rate generator period.

DS30292A-page 86

漏

1999 Microchip Technology Inc.