K9W8G08U1M

K9K4G08Q0M

K9K4G08U0M

K9K4G16Q0M

K9K4G16U0M

FLASH MEMORY

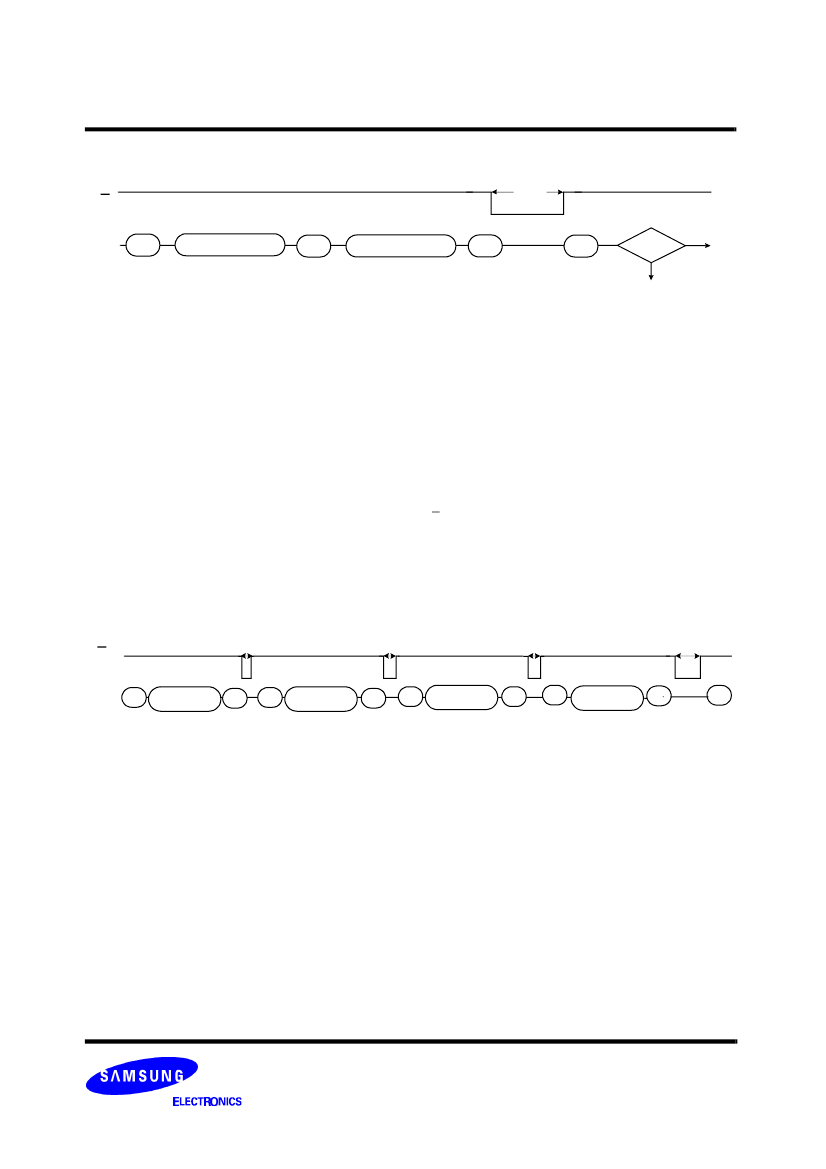

Figure 9. Random Data Input In a Page

t

PROG

R/B

"0"

I/Ox

80h

Address & Data Input

Col Add1,2 & Row Add1,2,3

Data

85h

Address & Data Input

Col Add1,2

Data

10h

70h

I/O

0

"1"

Fail

Pass

Cache Program

Cache Program is an extension of Page Program, which is executed with 2112byte(X8 device) or 1056word(X16 device) data regis-

ters, and is available only within a block. Since the device has 1 page of cache memory, serial data input may be executed while data

stored in data register are programmed into memory cell.

After writing the first set of data up to 2112byte(X8 device) or 1056word(X16 device) into the selected cache registers, Cache Pro-

gram command (15h) instead of actual Page Program (10h) is inputted to make cache registers free and to start internal program

operation. To transfer data from cache registers to data registers, the device remains in Busy state for a short period of time(tCBSY)

and has its cache registers ready for the next data-input while the internal programming gets started with the data loaded into data

registers. Read Status command (70h) may be issued to find out when cache registers become ready by polling the Cache-Busy sta-

tus bit(I/O 6). Pass/fail status of only the previouse page is available upon the return to Ready state. When the next set of data is

inputted with the Cache Program command, tCBSY is affected by the progress of pending internal programming. The programming of

the cache registers is initiated only when the pending program cycle is finished and the data registers are available for the transfer of

data from cache registers. The status bit(I/O5) for internal Ready/Busy may be polled to identify the completion of internal program-

ming. If the system monitors the progress of programming only with R/B, the last page of the target programming sequence must be

progammed with actual Page Program command (10h).

Figure 10. Cache Program

(available only within a block)

R/B

Address &

Data Input*

t

CBSY

t

CBSY

t

CBSY

t

PROG

80h

15h

80h

Address &

Data Input

15h

80h

Address &

Data Input

15h

80h

Col Add1,2 & Row Add1,2,3

Data

Col Add1,2 & Row Add1,2,3

Data

Col Add1,2 & Row Add1,2,3

Data

Address &

10h

Data Input

Col Add1,2 & Row Add1,2,3

Data

70h

32