PHY[5] MII receive data valid.

PHY[5] MII receive error. Strap option: PD (default) = 1522/1518 bytes;

PU = packet size up to 1536 bytes.

PHY[5] MII transmit clock. PHY mode MII

Serial bus configuration pin. See

鈥減in# 113.鈥?/div>

Serial bus configuration pin

If EEPROM is not present, the KS8995M will start itself with chip

default (00)...

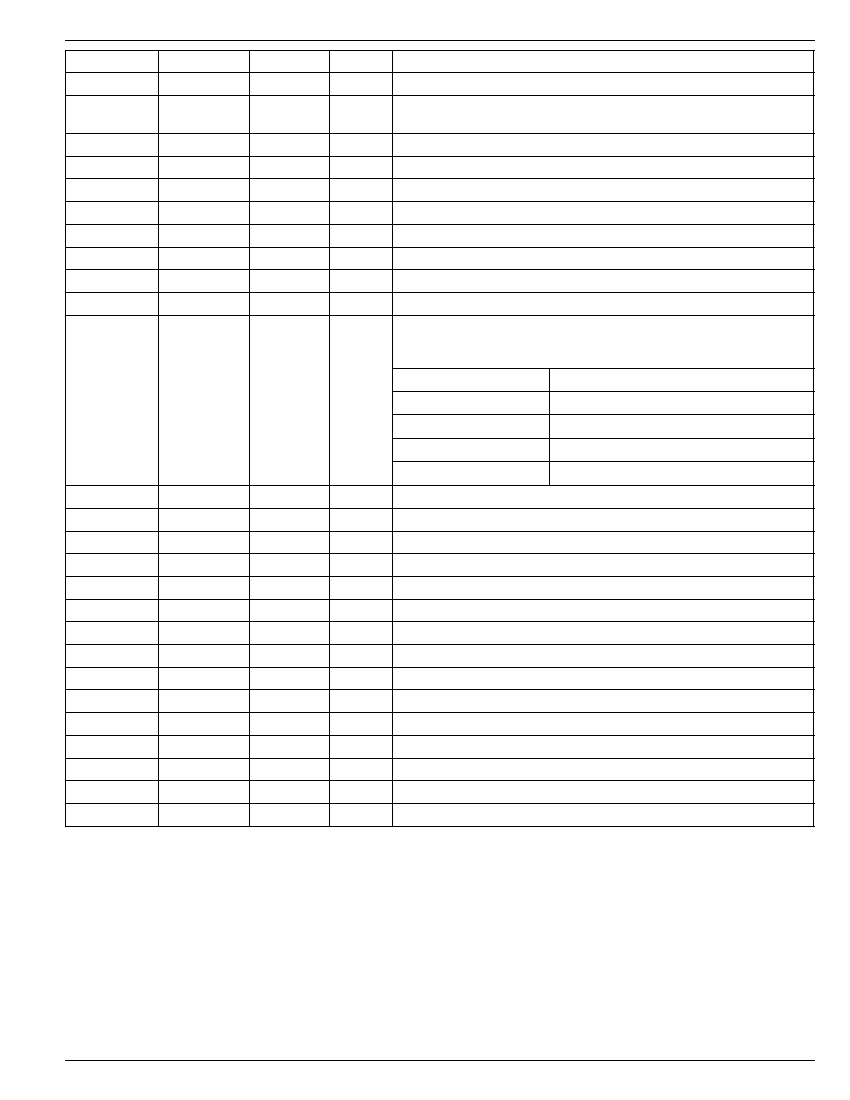

Pin Config.

PS[1:0]=00

PS[1:0]=01

PS[1:0]=10

PS[1:0]=11

Serial Bus Configuration

I2C Master Mode for EEPROM

Reserved

SPI Slave Mode for CPU Interface

Factory Test Mode (BIST)

47

48

115

5

11

20

26

33

4

10

19

25

32

119

84

PWRDN_N

RESERVE

RST_N

RXM1

RXM2

RXM3

RXM4

RXM5

RXP1

RXP2

RXP3

RXP4

RXP5

SCANEN

SCOL

Ipu

NC

Ipu

I

I

I

I

I

I

I

I

I

I

Ipd

Ipd/O

1

2

3

4

5

1

2

3

4

5

Full-chip power down. Active low.

Reserved pin. No connect.

Reset the KS8995M. Active low.

Physical receive signal - (differential)

Physical receive signal - (differential)

Physical receive signal - (differential)

Physical receive signal - (differential)

Physical receive signal - (differential)

Physical receive signal + (differential)

Physical receive signal + (differential)

Physical receive signal + (differential)

Physical receive signal + (differential)

Physical receive signal + (differential)

NC for normal operation. Factory test pin.

Switch MII collision detect.

Note:

1. P = Power supply

I = Input

O = Output

I/O = Bi-directional

Gnd = Ground

Ipu = Input w/ internal pull-up

Ipd = Input w/ internal pull-down

Ipd/O = Input w/ internal pull-down during reset, output pin otherwise

Ipu/O = Input w/ internal pull-up during reset, output pin otherwise

PU = Strap pin pull-up

PD = Strap pin pull-down

Otri = Output tristated

NC = No Connect

December 2003

17

M9999-120403