KS8995M

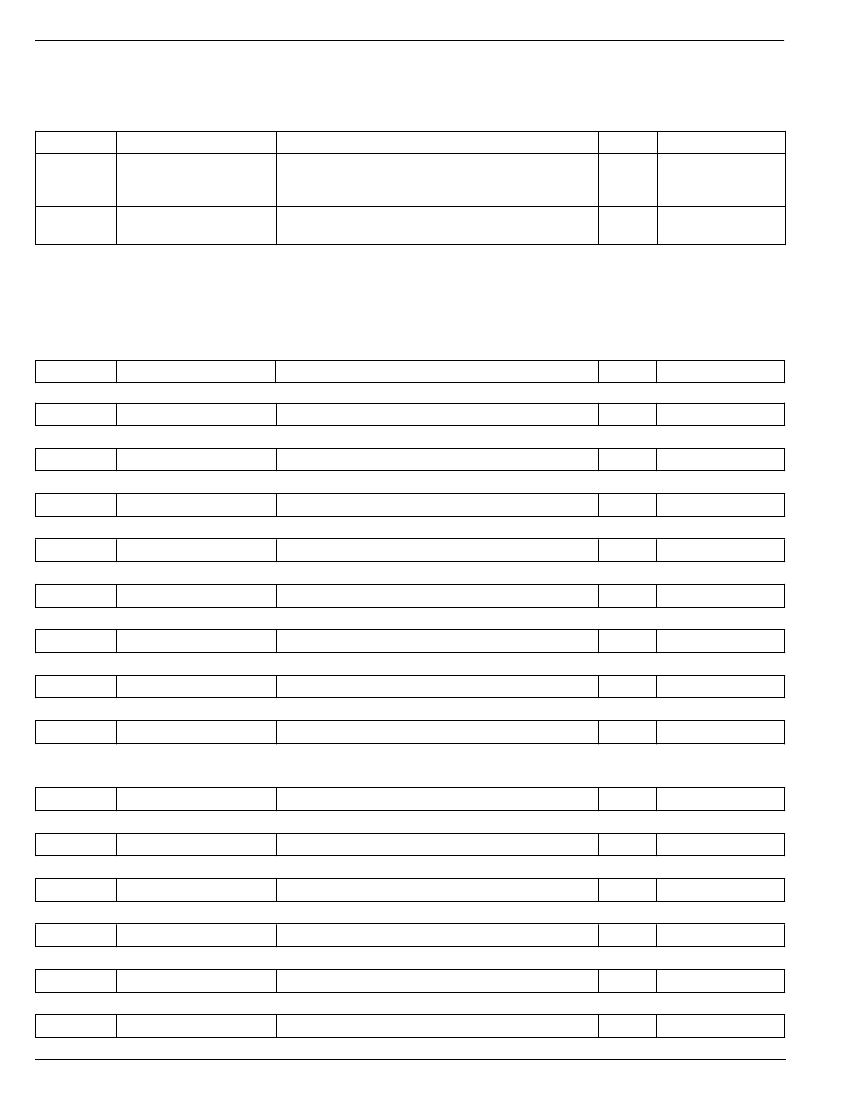

Register 31 (0x1F): Port 1 Status 1

Register 47 (0x2F): Port 2 Status 1

Register 63 (0x3F): Port 3 Status 1

Register 79 (0x4F): Port 4 Status 1

Register 95 (0x5F): Port 5 Status 1

Address

7-1

Name

Reserved

Description

1, perform PHY loopback, i.e. loopback MAC鈥檚 TX

back to RX.

0, normal operation.

1, Far end fault status detected.

0, no far end fault status detected.

Mode

R/O

Default

0

Micrel

0

Far end fault

RO

0

Advanced Control Registers

The IPv4 TOS priority control registers implement a fully decoded 64 bit DSCP (Differentiated Services Code Point) register

used to determine priority from the 6 bit TOS field in the IP header. The most significant 6 bits of the TOS field are fully decoded

into 64 possibilities, and the singular code that results is compared against the corresponding bit in the DSCP register. If the

register bit is a 1, the priority is high; if it is a 0, the priority is low.

Address

Name

Description

Mode

Default

Register 96 (0x60): TOS Priority Control Register 0

7-0

DSCP[63:56]

R/W

00000000

Register 97 (0x61): TOS Priority Control Register 1

7-0

DSCP[55:48]

R/W

00000000

Register 98 (0x62): TOS Priority Control Register 2

7-0

DSCP[47:40]

R/W

00000000

Register 99 (0x63): TOS Priority Control Register 3

7-0

DSCP[39:32]

R/W

00000000

Register 100 (0x64): TOS Priority Control Register 4

7-0

DSCP[31:24]

R/W

00000000

Register 101 (0x65): TOS Priority Control Register 5

7-0

DSCP[23:16]

R/W

00000000

Register 102 (0x66): TOS Priority Control Register 6

7-0

DSCP[15:8]

R/W

00000000

Register 103 (0x67): TOS Priority Control Register 7

7-0

DSCP[7:0]

R/W

00000000

Registers 104 to 109 define the switching engine鈥檚 MAC address. This 48-bit address is used as the source address in MAC pause control frames.

Register 104 (0x68): MAC Address Register 0

7-0

MACA[47:40]

R/W

0x00

Register 105 (0x69): MAC Address Register 1

7-0

MACA[39:32]

R/W

0x10

Register 106 (0x6A): MAC Address Register 2

7-0

MACA[31:24]

R/W

0xA1

Register 107 (0x6B): MAC Address Register 3

7-0

MACA[23:16]

R/W

0xff

Register 108 (0x6C): MAC Address Register 4

7-0

MACA[15:8]

R/W

0xff

Register 109 (0X6D): MAC Address Register 5

7-0

MACA[7:0]

R/W

0xff

Use registers 110 and 111 to read or write data to the static MAC address table, VLAN table, dynamic address table, or the MIB counters.

M9999-120403

50

December 2003