KS8995M

Micrel

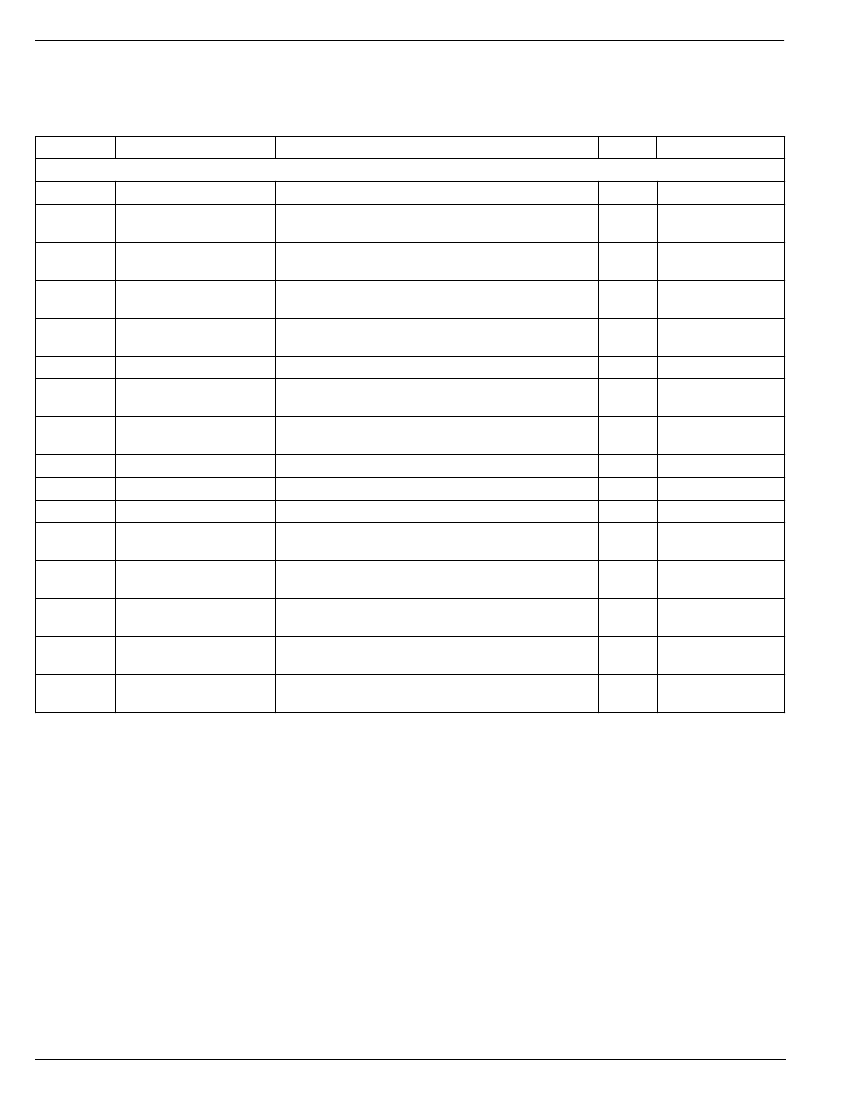

MIIM Registers

(All the registers defined in this section can be also accessed via the SPI interface. Note: different mapping mechanisms used

for MIIM and SPI). The 鈥淧HYAD鈥?defined in IEEE is assigned as 鈥?x1鈥?for port 1, 鈥?x2鈥?for port 2, 鈥?x3鈥?for port 3, 鈥?x4鈥?for port

4, 鈥?x5鈥?for port 5. The 鈥淩EGAD鈥?supported are 0,1,2,3,4,5.

Address

Name

Description

Mode

Default

Register 0: MII Control

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

Soft reset

Loop back

Force 100

AN enable

Power down

PHY Isolate

Restart AN

Force full-duplex

Collision test

Reserved

Reserved

Force MDI

Disable Auto MDI/MDIX

Disable far end fault

Disable transmit

Disable LED

1, Force MDI

0, Normal operation

1, Disable auto MDI/MDIX

0, Normal operation

1, Disable far end fault detection

0, Normal operation

1, Disable transmit

0, Normal operation

1, Disable LED

0, Normal operation

Not supported

1, Loop back mode (loop back at MAC)

0, Normal operation

1, 100Mbps

0, 10Mbps

1, Auto-negotiation enabled

0, Auto-negotiation disabled

1, Power down

0, Normal operation

Not supported

1, Restart auto-negotiation

0, Normal operation

1, Full duplex

0, Half-duplex

NOT SUPPORTED

RO

R/W

R/W

R/W

R/W

RO

R/W

R/W

RO

RO

RO

R/W

R/W

R/W

R/W

R/W

0

0

1

1

0

0

0

0

0

0

0

0

0

0

0

0

M9999-120403

60

December 2003