Freescale Semiconductor, Inc.

TN

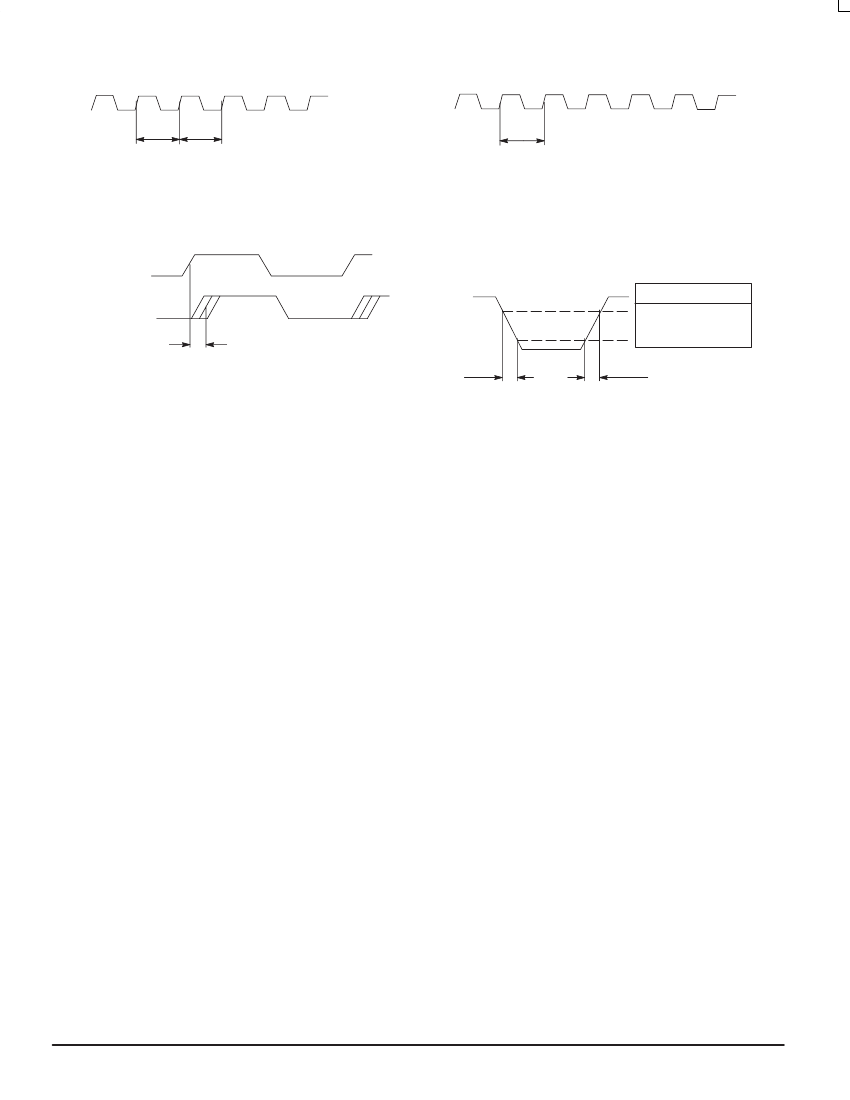

TN+1

TJIT(CC) =

|T

N 鈥揟N+1

|

T0

TJIT(P) =

|T

N 鈥?/f0

|

The variation in cycle time of a signal between adjacent cycles, over a

random sample of adjacent cycle pairs

The deviation in cycle time of a signal with respect to the ideal period over

a random sample of cycles

Figure 17. Cycle鈥搕o鈥揷ycle Jitter

Figure 18. Period Jitter

CCLK

(PCLK)

FB_IN

VCC=3.3 V

2.4

0.55

TJIT(鈭? =

|T

0 鈥揟1 mean|

The deviation in t0 for a controlled edge with respect to a t0 mean in a

random sample of cycles

tF

tR

VCC=2.5 V

1.8 V

0.6 V

Freescale Semiconductor, Inc...

Figure 19. I/O Jitter

Figure 20. Output Transition Time Test Reference

MOTOROLA

For More Information On This Product,

12

Go to: www.freescale.com

TIMING SOLUTIONS