PIC16CE62X

4.4

Indirect Addressing, INDF and FSR

Registers

A simple program to clear RAM location 20h-2Fh using

indirect addressing is shown in Example 4-1.

The INDF register is not a physical register. Addressing

the INDF register will cause indirect addressing.

Indirect addressing is possible by using the INDF reg-

ister. Any instruction using the INDF register actually

accesses data pointed to by the 铿乴e select register

(FSR). Reading INDF itself indirectly will produce 00h.

Writing to the INDF register indirectly results in a

no-operation (although status bits may be affected). An

effective 9-bit address is obtained by concatenating the

8-bit FSR register and the IRP bit (STATUS<7>), as

shown in Figure 4-13. However, IRP is not used in the

PIC16CE62X.

EXAMPLE 4-1:

movlw

movwf

NEXT

clrf

incf

btfss

goto

CONTINUE:

INDIRECT ADDRESSING

0x20

FSR

INDF

FSR

FSR,4

NEXT

;initialize pointer

;to RAM

;clear INDF register

;inc pointer

;all done?

;no clear next

;yes continue

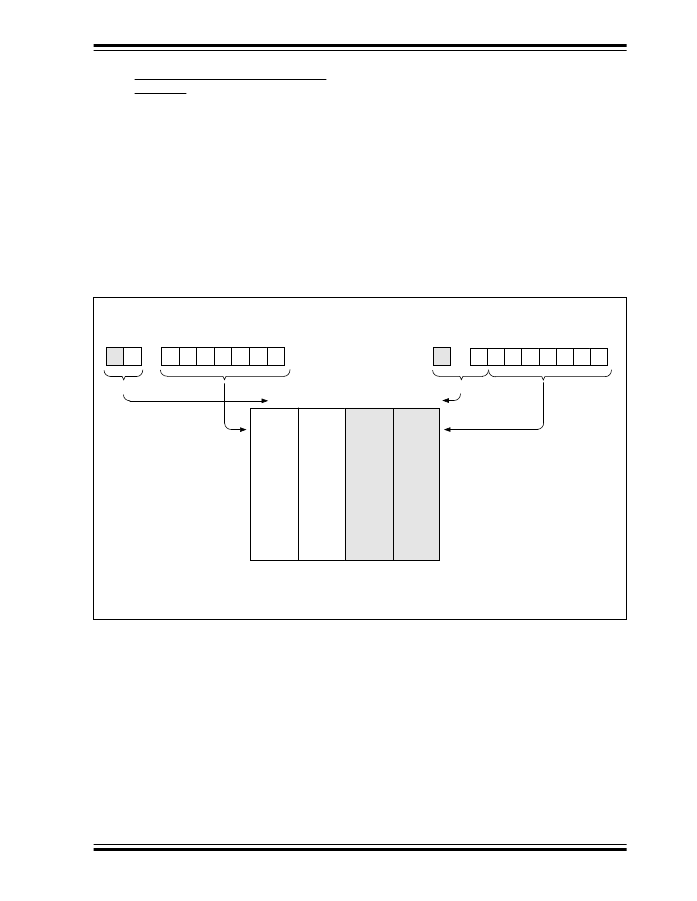

FIGURE 4-13: DIRECT/INDIRECT ADDRESSING PIC16CE62X

Direct Addressing

(1)

RP1

Indirect Addressing

0

IRP

(1)

7

FSR register

0

RP0

6

from opcode

bank select

location select

00

00h

01

10

11

bank select

00h

location select

not used

Data

Memory

7Fh

7Fh

Bank 0

Bank 1

Bank 2

Bank 3

For memory map detail see Figure 4-4 and Figure 4-5.

Note 1: The RP1 and IRP bits are reserved, always maintain these bits clear.

漏

1998 Microchip Technology Inc.

Preliminary

DS40182A-page 21