PIC16CE62X

10.4.5

TIME-OUT SEQUENCE

10.4.6

On power-up the time-out sequence is as follows: First

PWRT time-out is invoked after POR has expired. Then

OST is activated. The total time-out will vary based on

oscillator con铿乬uration and PWRTE bit status. For

example, in RC mode with PWRTE bit erased (PWRT

disabled), there will be no time-out at all. Figure 10-9,

Figure 10-10 and Figure 10-11 depict time-out

sequences.

Since the time-outs occur from the POR pulse, if MCLR

is kept low long enough, the time-outs will expire. Then

bringing MCLR high will begin execution immediately

(see Figure 10-10). This is useful for testing purposes

or to synchronize more than one PICmicro device oper-

ating in parallel.

Table 10-5 shows the reset conditions for some special

registers, while Table 10-6 shows the reset conditions

for all the registers.

POWER CONTROL (PCON)/STATUS

REGISTER

The power control/status register, PCON (address

8Eh) has two bits.

Bit0 is BO (Brown-out). BO is unknown on

power-on-reset. It must then be set by the user and

checked on subsequent resets to see if BO = 0

indicating that a brown-out has occurred. The BO

status bit is a don鈥檛 care and is not necessarily

predictable if the brown-out circuit is disabled (by

setting BODEN bit = 0 in the Con铿乬uration word).

Bit1 is POR (Power-on-reset). It is a 鈥?鈥?on

power-on-reset and unaffected otherwise. The user

must write a 鈥?鈥?to this bit following a power-on-reset.

On a subsequent reset if POR is 鈥?鈥? it will indicate that

a power-on-reset must have occurred (V

DD

may have

gone too low).

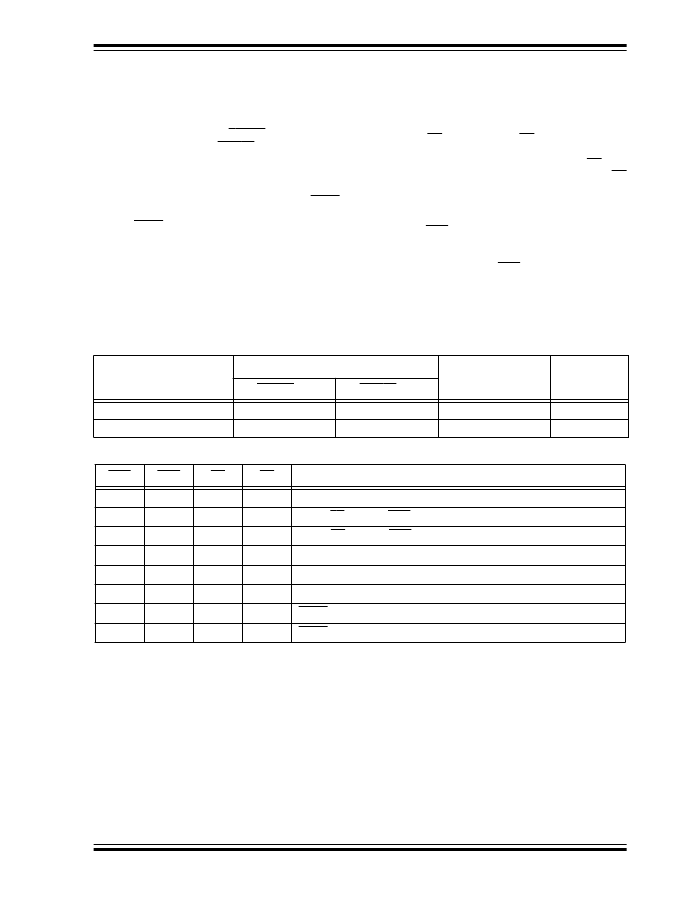

TABLE 10-3:

TIME-OUT IN VARIOUS SITUATIONS

Power-up

Brown-out Reset

PWRTE = 0

PWRTE = 1

1024 T

OSC

鈥?/div>

72 ms + 1024 T

OSC

72 ms

72 ms + 1024 T

OSC

72 ms

Wake-up

from SLEEP

1024 T

OSC

鈥?/div>

Oscillator Con铿乬uration

XT, HS, LP

RC

TABLE 10-4:

POR

STATUS/PCON BITS AND THEIR SIGNIFICANCE

TO

PD

BOR

0

0

0

1

1

1

1

1

X

X

X

0

1

1

1

1

1

0

X

X

0

0

u

1

1

X

0

X

1

0

u

0

Power-on-reset

Illegal, TO is set on POR

Illegal, PD is set on POR

Brown-out Reset

WDT Reset

WDT Wake-up

MCLR reset during normal operation

MCLR reset during SLEEP

漏

1998 Microchip Technology Inc.

Preliminary

DS40182A-page 55