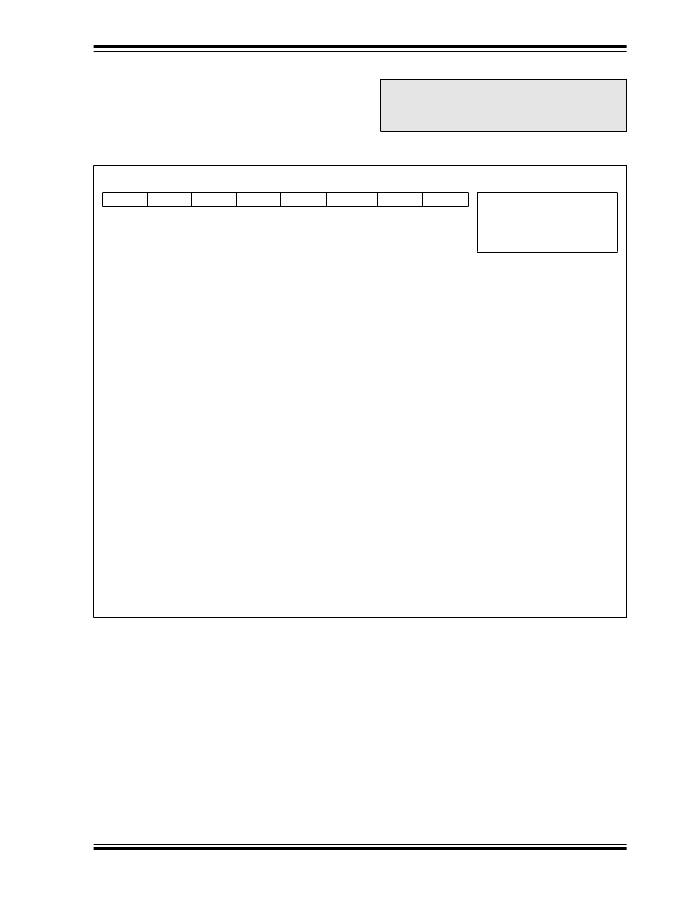

enable bit, GIE (INTCON<7>).

interrupt sources.

read as 鈥?鈥?/div>

- n = Value at POR reset

R/W-0

EEIE

bit 7:

GIE:

Global Interrupt Enable bit

1 = Enables all un-masked interrupts

0 = Disables all interrupts

Note:

For the operation of the interrupt structure, please refer to Section 8.5.

EEIE:

EE Write Complete Interrupt Enable bit

1 = Enables the EE write complete interrupt

0 = Disables the EE write complete interrupt

T0IE:

TMR0 Over铿俹w Interrupt Enable bit

1 = Enables the TMR0 interrupt

0 = Disables the TMR0 interrupt

INTE:

RB0/INT Interrupt Enable bit

1 = Enables the RB0/INT interrupt

0 = Disables the RB0/INT interrupt

RBIE:

RB Port Change Interrupt Enable bit

1 = Enables the RB port change interrupt

0 = Disables the RB port change interrupt

T0IF:

TMR0 over铿俹w interrupt 铿俛g bit

1 = TMR0 has over铿俹wed (must be cleared in software)

0 = TMR0 did not over铿俹w

INTF:

RB0/INT Interrupt Flag bit

1 = The RB0/INT interrupt occurred

0 = The RB0/INT interrupt did not occur

RBIF:

RB Port Change Interrupt Flag bit

1 = When at least one of the RB7:RB4 pins changed state (must be cleared in software)

0 = None of the RB7:RB4 pins have changed state

bit 6:

bit 5:

bit 4:

bit 3:

bit 2:

bit 1:

bit 0:

漏

1998 Microchip Technology Inc.

DS30430C-page 17