鈥?/div>

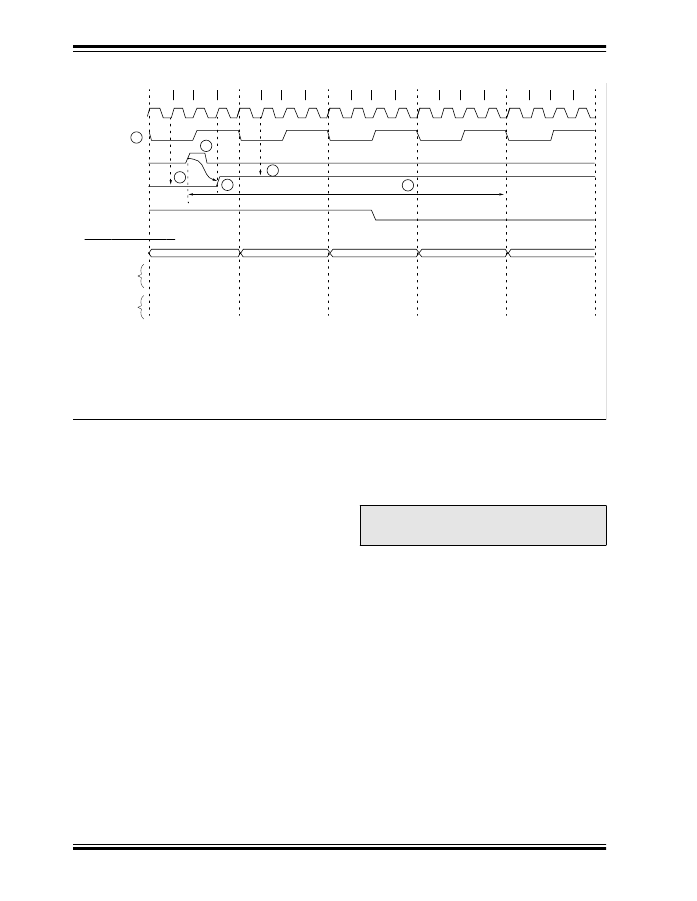

Dummy Cycle

0004h

Inst (0004h)

Dummy Cycle

0005h

Inst (0005h)

Inst (0004h)

1

5

Q2

Q3

Q4

Q1

Q2

Q3

Q4

Q1

Q2

Q3

Q4

Q1

Q2

Q3

Q4

Q1

Q2

Q3

Q4

4

1

Interrupt Latency 2

Note 1: INTF 铿俛g is sampled here (every Q1).

2: Interrupt latency = 3-4Tcy where Tcy = instruction cycle time.

Latency is the same whether Inst (PC) is a single cycle or a 2-cycle instruction.

3: CLKOUT is available only in RC oscillator mode.

4: For minimum width of INT pulse, refer to AC specs.

5: INTF is enabled to be set anytime during the Q4-Q1 cycles.

8.9.1

INT INTERRUPT

8.9.3

PORT RB INTERRUPT

External interrupt on RB0/INT pin is edge triggered:

either rising if INTEDG bit (OPTION_REG<6>) is set,

or falling, if INTEDG bit is clear. When a valid edge

appears on the RB0/INT pin, the INTF bit

(INTCON<1>) is set. This interrupt can be disabled by

clearing control bit INTE (INTCON<4>). Flag bit INTF

must be cleared in software via the interrupt service

routine before re-enabling this interrupt. The INT

interrupt can wake the processor from SLEEP

(Section 8.12) only if the INTE bit was set prior to going

into SLEEP. The status of the GIE bit decides whether

the processor branches to the interrupt vector

following wake-up.

8.9.2

TMR0 INTERRUPT

An input change on PORTB<7:4> sets 铿俛g bit RBIF

(INTCON<0>). The interrupt can be enabled/disabled

by setting/clearing enable bit RBIE (INTCON<3>)

(Section 5.2).

Note 1:

For a change on the I/O pin to be

recognized, the pulse width must be at

least T

CY

wide.

An over铿俹w (FFh

鈫?/div>

00h) in TMR0 will set 铿俛g bit T0IF

(INTCON<2>). The interrupt can be enabled/disabled

by setting/clearing enable bit T0IE (INTCON<5>)

(Section 6.0).

DS30430C-page 48

漏

1998 Microchip Technology Inc.