鈫?/div>

GIE

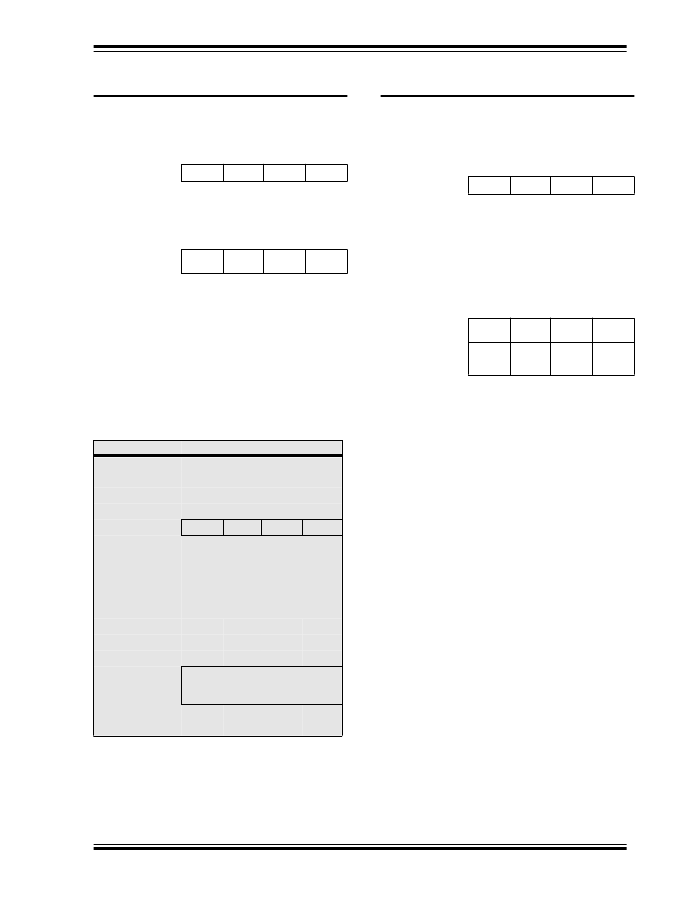

None

00

0000

0000

1001

Return from Interrupt. Stack is POPed

and Top of Stack (TOS) is loaded in the

PC. Interrupts are enabled by setting

Global Interrupt Enable bit, GIE

(INTCON<7>). This is a two cycle

instruction.

NOP

RETFIE

No operation.

Q2

Q3

Q4

Words:

No-Opera No-Opera No-Operat

tion

tion

ion

1

2

Q1

Decode

Example

NOP

Cycles:

Q Cycle Activity:

1st Cycle

2nd Cycle

Q2

No-Opera

tion

Q3

Set the

GIE bit

Q4

Pop from

the Stack

No-Operat

ion

No-Opera No-Opera No-Operat

tion

tion

ion

Example

RETFIE

After Interrupt

PC =

GIE =

TOS

1

OPTION

Syntax:

Operands:

Operation:

Encoding:

Description:

Load Option Register

[

label

]

None

(W)

鈫?/div>

OPTION

00

0000

0110

0010

OPTION

Status Affected: None

The contents of the W register are

loaded in the OPTION register. This

instruction is supported for code com-

patibility with PIC16C5X products.

Since OPTION is a readable/writable

register, the user can directly address

it.

Words:

Cycles:

Example

1

1

To maintain upward compatibility

with future PIC16CXX products,

do not use this instruction.

漏

1998 Microchip Technology Inc.

DS30430C-page 63