PIC16F8X

8.4

Power-on Reset (POR)

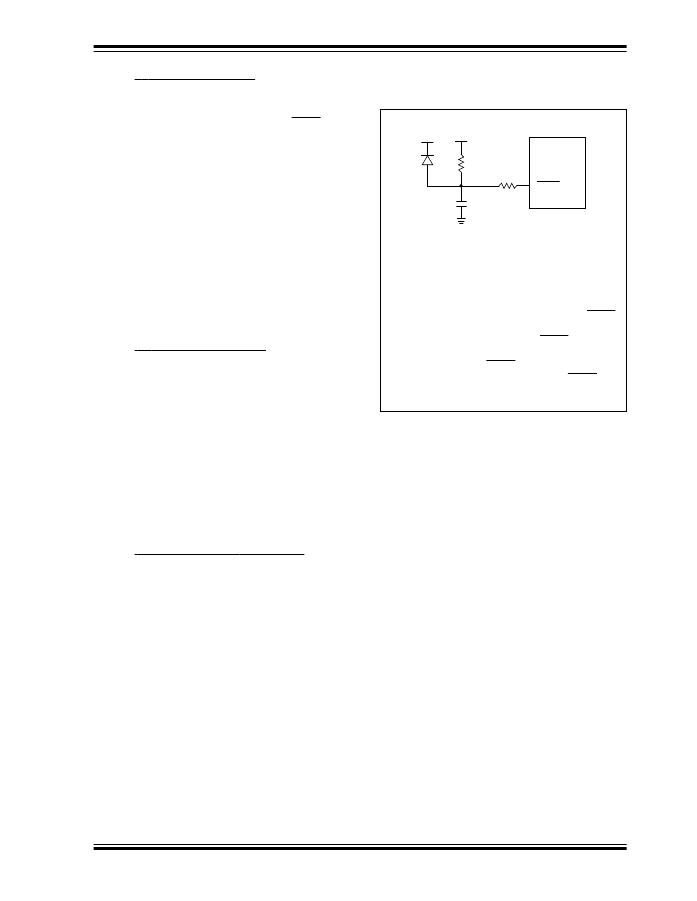

FIGURE 8-9:

A Power-on Reset pulse is generated on-chip when

V

DD

rise is detected (in the range of 1.2V - 1.7V). To

take advantage of the POR, just tie the MCLR pin

directly (or through a resistor) to V

DD

. This will eliminate

external RC components usually needed to create

Power-on Reset. A minimum rise time for V

DD

must be

met for this to operate properly. See Electrical Speci铿?

cations for details.

When the device starts normal operation (exits the

reset condition), device operating parameters (voltage,

frequency, temperature, ...) must be meet to ensure

operation. If these conditions are not met, the device

must be held in reset until the operating conditions

are met.

For additional information, refer to Application Note

AN607, "Power-up

Trouble Shooting."

The POR circuit does not produce an internal reset

when V

DD

declines.

EXTERNAL POWER-ON

RESET CIRCUIT (FOR SLOW

V

DD

POWER-UP)

V

DD

V

DD

D

R

R1

MCLR

C

PIC16FXX

8.5

Power-up Timer (PWRT)

The Power-up Timer (PWRT) provides a 铿亁ed 72 ms

nominal time-out (T

PWRT

) from POR (Figure 8-10,

Figure 8-11, Figure 8-12 and Figure 8-13). The

Power-up Timer operates on an internal RC oscillator.

The chip is kept in reset as long as the PWRT is active.

The PWRT delay allows the V

DD

to rise to an accept-

able level (Possible exception shown in Figure 8-13).

A con铿乬uration bit, PWRTE, can enable/disable the

PWRT. See either Figure 8-1 or Figure 8-2 for the oper-

ation of the PWRTE bit for a particular device.

The power-up time delay T

PWRT

will vary from chip to

chip due to V

DD

, temperature, and process variation.

See DC parameters for details.

Note 1: External Power-on Reset circuit is required

only if V

DD

power-up rate is too slow. The

diode D helps discharge the capacitor

quickly when V

DD

powers down.

2: R < 40 k鈩?is recommended to make sure

that voltage drop across R does not exceed

0.2V (max leakage current spec on MCLR

pin is 5

碌A).

A larger voltage drop will

degrade V

IH

level on the MCLR pin.

3: R1 = 100鈩?to 1 k鈩?will limit any current

铿俹wing into MCLR from external

capacitor C in the event of an MCLR pin

breakdown due to ESD or EOS.

8.6

Oscillator Start-up Timer (OST)

The Oscillator Start-up Timer (OST) provides a 1024

oscillator cycle delay (from OSC1 input) after the

PWRT delay ends (Figure 8-10, Figure 8-11,

Figure 8-12 and Figure 8-13). This ensures the crystal

oscillator or resonator has started and stabilized.

The OST time-out (T

OST

) is invoked only for XT, LP and

HS modes and only on Power-on Reset or wake-up

from SLEEP.

When V

DD

rises very slowly, it is possible that the

T

PWRT

time-out and T

OST

time-out will expire before

V

DD

has reached its 铿乶al value. In this case

(Figure 8-13), an external power-on reset circuit may

be necessary (Figure 8-9).

漏

1998 Microchip Technology Inc.

DS30430C-page 43