Philips Semiconductors

SC16C754

Quad UART with 64-byte FIFO

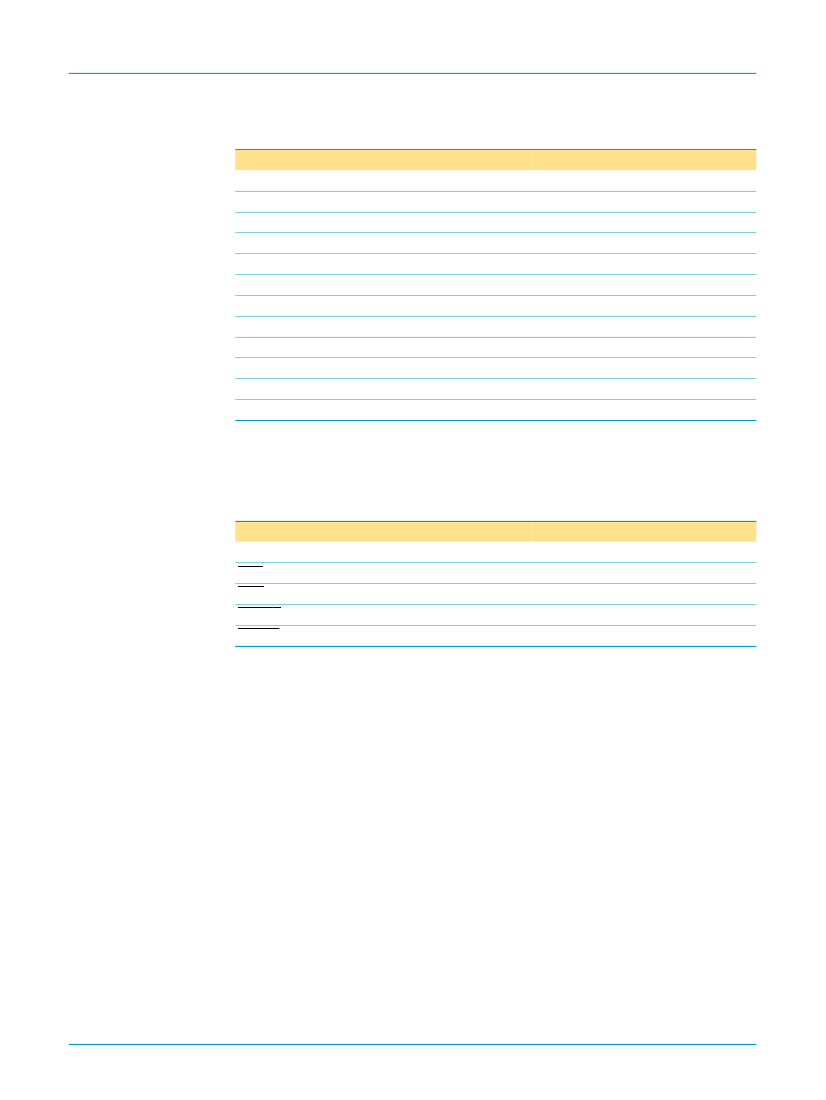

Register reset functions

Reset control

RESET

RESET

RESET

RESET

RESET

RESET

RESET

RESET

RESET

RESET

RESET

RESET

Reset state

All bits cleared.

Bit 0 is set. All other bits cleared.

All bits cleared.

Reset to 00011101 (1D hex).

All bits cleared.

Bits 5 and 6 set. All other bits cleared.

Bits 0-3 cleared. Bits 4-7 input signals.

All bits cleared.

Pointer logic cleared.

Pointer logic cleared.

All bits cleared.

All bits cleared.

Table 4:

Register

Interrupt enable register

Interrupt identi铿乧ation register

FIFO control register

Line control register

Modem control register

Line status register

Modem status register

Enhanced feature register

Receiver holding register

Transmitter holding register

Transmission control register

Trigger level register

[1]

Registers DLL, DLH, SPR, Xon1, Xon2, Xoff1, Xoff2 are not reset by the top-level reset signal

RESET, i.e., they hold their initialization values during reset.

Table 5

summarizes the state of registers after reset.

Table 5:

Signal

TX

RTS

DTR

RXRDY

TXRDY

Signal RESET functions

Reset control

RESET

RESET

RESET

RESET

RESET

Reset state

high

high

high

high

low

9397 750 11618

漏 Koninklijke Philips Electronics N.V. 2003. All rights reserved.

Product data

Rev. 04 鈥?19 June 2003

13 of 49