Philips Semiconductors

SC16C754

Quad UART with 64-byte FIFO

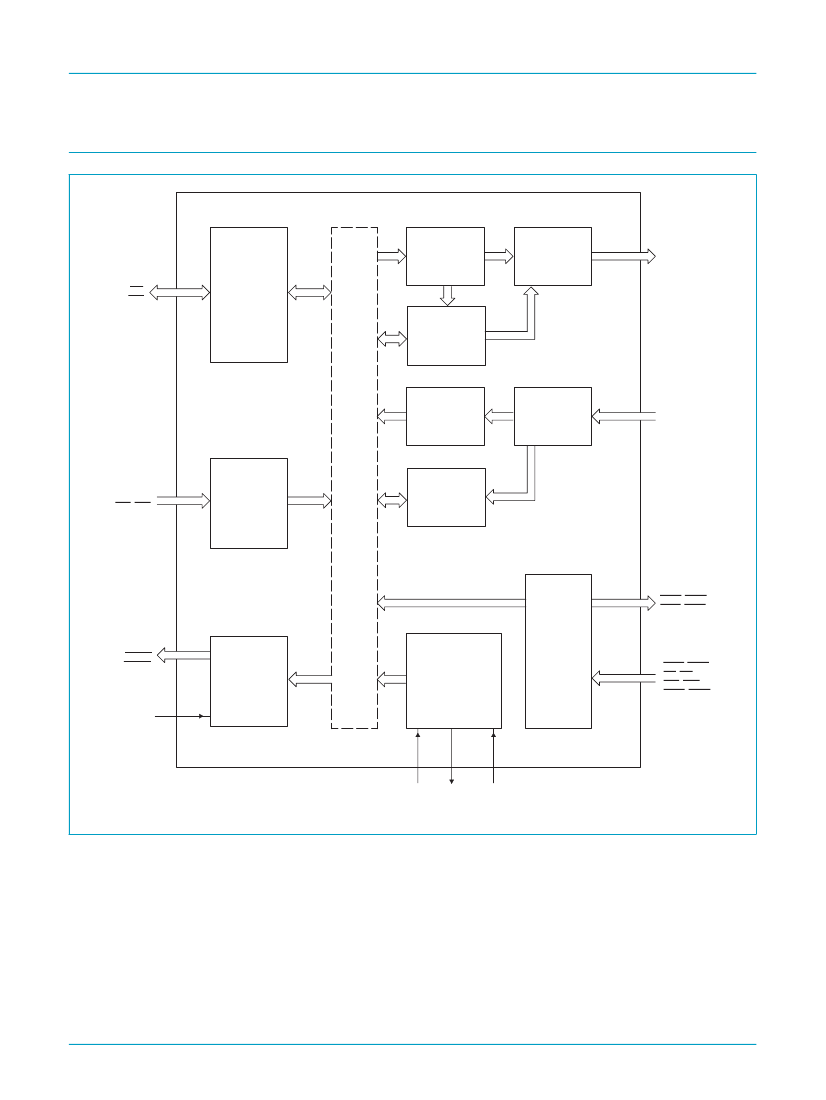

4. Block diagram

SC16C754

TRANSMIT

FIFO

REGISTERS

D0鈥揇7

IOR

IOW

RESET

DATA BUS

AND

CONTROL LOGIC

FLOW

CONTROL

LOGIC

TRANSMIT

SHIFT

REGISTER

TXA-TXD

INTERCONNECT BUS LINES

AND

CONTROL SIGNALS

RECEIVE

FIFO

REGISTERS

RECEIVE

SHIFT

REGISTER

RXA-RXD

A0鈥揂2

CSA-CSD

REGISTER

SELECT

LOGIC

FLOW

CONTROL

LOGIC

DTRA-DTRD

RTSA-RTSD

INTA-INTD

TXRDY

RXRDY

INTERRUPT

CONTROL

LOGIC

INTSEL

MODEM

CONTROL

LOGIC

CLOCK AND

BAUD RATE

GENERATOR

CTSA-CTSD

RIA-RID

CDA-CDD

DSRA-DSRD

002aaa206

XTAL1

XTAL2

CLKSEL

Fig 1. Block diagram.

9397 750 11618

漏 Koninklijke Philips Electronics N.V. 2003. All rights reserved.

Product data

Rev. 04 鈥?19 June 2003

3 of 49