Philips Semiconductors

SC16C754

Quad UART with 64-byte FIFO

6.5.1

Interrupt mode operation

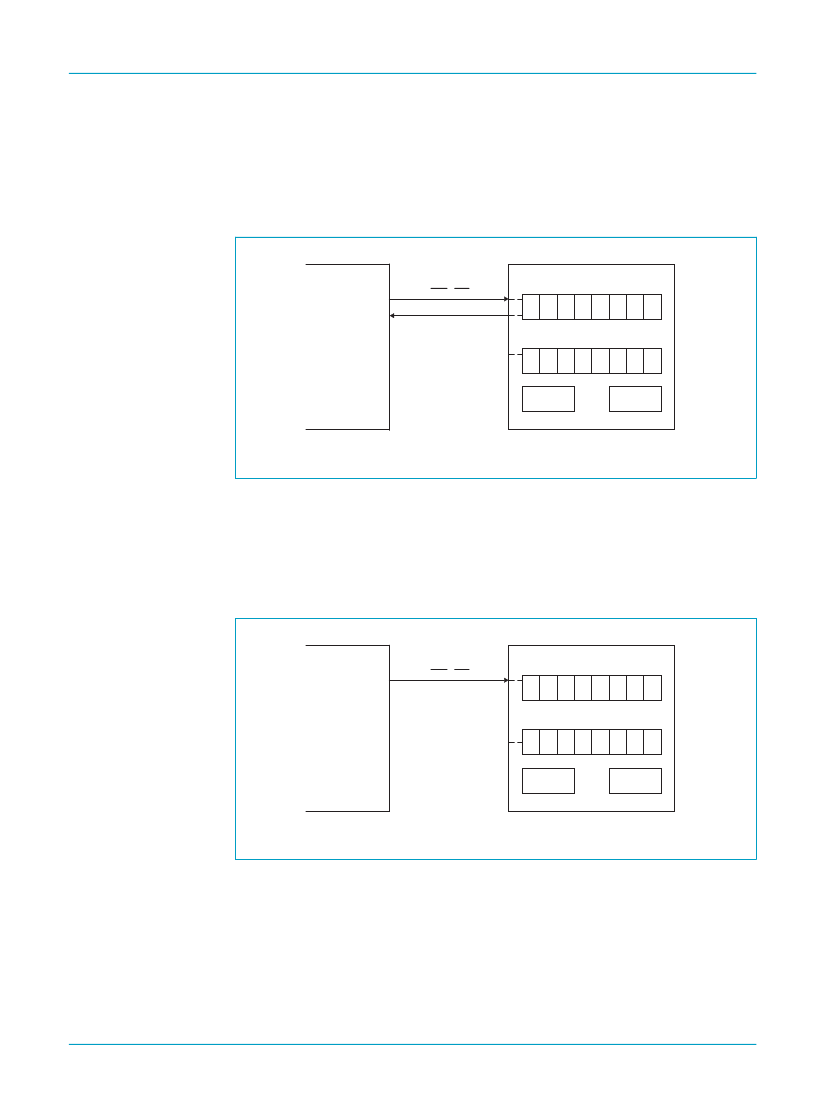

In interrupt mode (if any bit of IER[3:0] is 1) the processor is informed of the status of

the receiver and transmitter by an interrupt signal, INT. Therefore, it is not necessary

to continuously poll the line status register (LSR) to see if any interrupt needs to be

serviced.

Figure 8

shows interrupt mode operation.

IOW / IOR

INT

PROCESSOR

IIR

IER

1

1

1

1

THR

RHR

002aaa230

Fig 8. Interrupt mode operation.

6.5.2

Polled mode operation

In polled mode (IER[3:0] = 0000) the status of the receiver and transmitter can be

checked by polling the line status register (LSR). This mode is an alternative to the

FIFO interrupt mode of operation where the status of the receiver and transmitter is

automatically known by means of interrupts sent to the CPU.

Figure 9

shows FIFO

polled mode operation.

IOW / IOR

PROCESSOR

LSR

IER

0

0

0

0

THR

RHR

002aaa231

Fig 9. FIFO polled mode operation.

9397 750 11618

漏 Koninklijke Philips Electronics N.V. 2003. All rights reserved.

Product data

Rev. 04 鈥?19 June 2003

15 of 49