Philips Semiconductors

SC16C754

Quad UART with 64-byte FIFO

6.5 Interrupts

The SC16C754 has interrupt generation and prioritization (six prioritized levels of

interrupts) capability. The interrupt enable register (IER) enables each of the six types

of interrupts and the INT signal in response to an interrupt generation. The IER can

also disable the interrupt system by clearing bits 0-3, 5-7. When an interrupt is

generated, the IIR indicates that an interrupt is pending and provides the type of

interrupt through IIR[5;0].

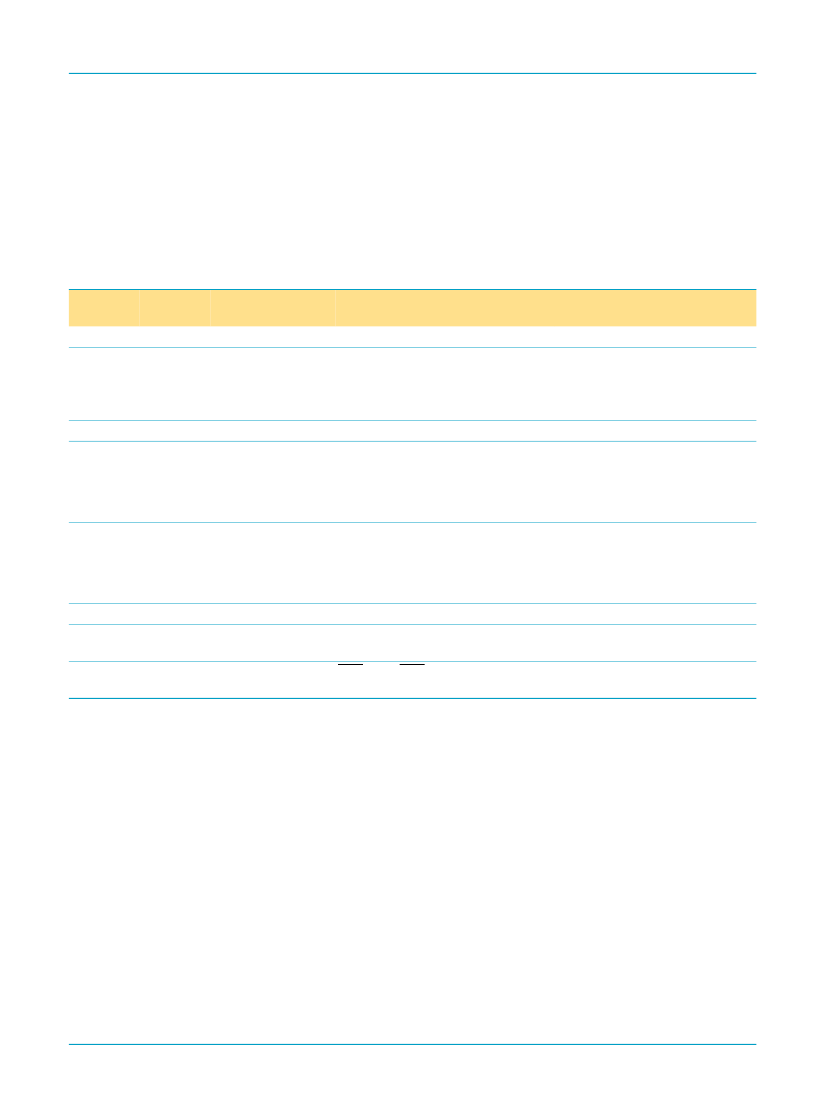

Table 6

summarizes the interrupt control functions.

Table 6:

IIR[5:0]

000001

000110

Interrupt control functions

Priority

level

None

1

Interrupt type

none

receiver line status

Interrupt source

none

OE, FE, PE, or BI errors occur in

characters in the RX FIFO

Interrupt reset method

none

FE, PE, BI: all erroneous

characters are read from the

RX FIFO.

OE: read LSR

001100

000100

2

2

RX time-out

RHR interrupt

stale data in RX FIFO

DRDY (data ready)

(FIFO disable)

RX FIFO above trigger level

(FIFO enable)

000010

3

THR interrupt

TFE (THR empty)

(FIFO disable)

TX FIFO passes above trigger level

(FIFO enable)

000000

010000

100000

4

5

6

modem status

Xoff interrupt

CTS, RTS

MSR[3:0] = 0

receive Xoff character(s)/special

character

read MSR

receive Xon character(s)/Read of

IIR

read IIR

or

a write to the THR

read RHR

read RHR

RTS pin or CTS pin change state from read IIR

active (LOW) to inactive (HIGH)

It is important to note that for the framing error, parity error, and break conditions,

LSR[7] generates the interrupt. LSR[7] is set when there is an error anywhere in the

RX FIFO, and is cleared only when there are no more errors remaining in the FIFO.

LSR[4:2] always represent the error status for the received character at the top of the

RX FIFO. Reading the RX FIFO updates LSR[4:2] to the appropriate status for the

new character at the top of the FIFO. If the RX FIFO is empty, then LSR[4:2] are all

zeros.

For the Xoff interrupt, if an Xoff 铿俹w character detection caused the interrupt, the

interrupt is cleared by an Xon 铿俹w character detection. If a special character

detection caused the interrupt, the interrupt is cleared by a read of the LSR.

9397 750 11618

漏 Koninklijke Philips Electronics N.V. 2003. All rights reserved.

Product data

Rev. 04 鈥?19 June 2003

14 of 49