铮?/div>

prescaler

divisor =

--------------------------------------------------------------------------------

-

(

desired baud rate

脳

16

)

Where:

prescaler = 1, when MCR[7] is set to 0 after reset (divide-by-1 clock selected)

prescaler = 4, when MCR[7] is set to 1 after reset (divide-by-4 clock selected).

Remark:

The default value of prescaler after reset is divide-by-1.

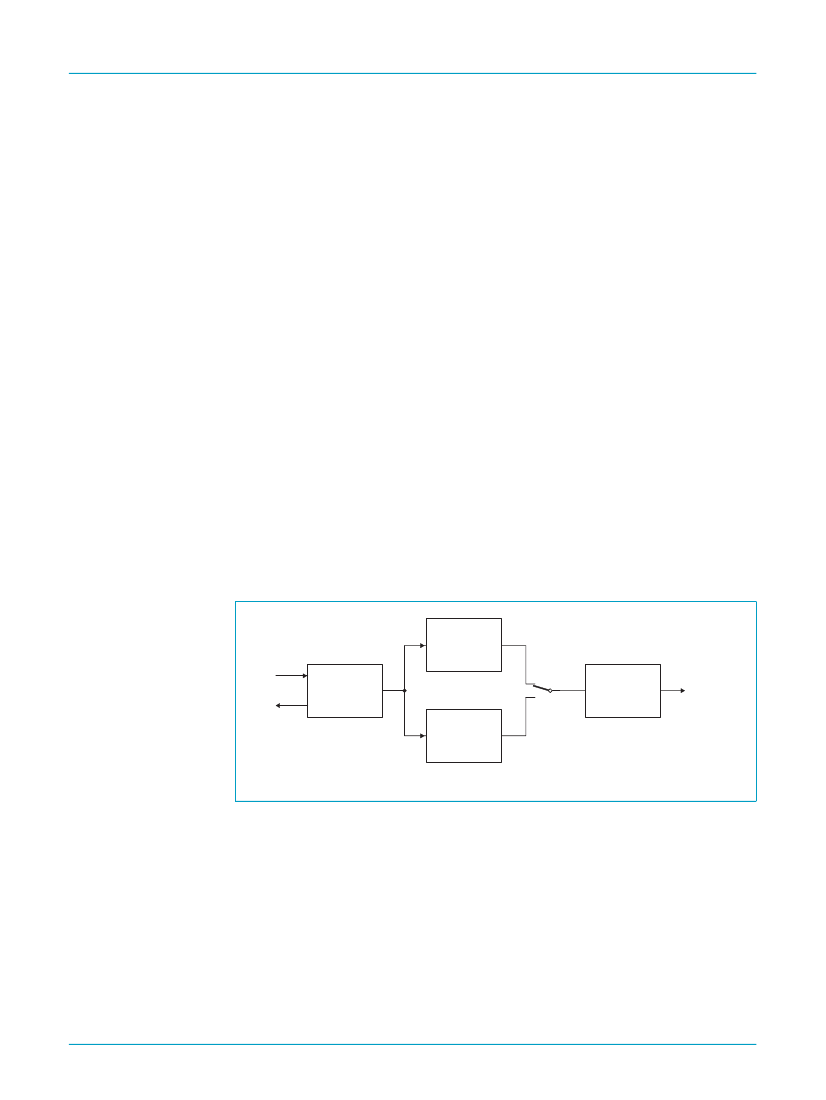

Figure 12

shows the internal prescaler and baud rate generator circuitry.

PRESCALER

LOGIC

(DIVIDE-BY-1)

XTAL1

INTERNAL

OSCILLATOR

LOGIC

MCR[7] = 0

INTERNAL

BAUD RATE

CLOCK FOR

TRANSMITTER

AND

RECEIVER

INPUT CLOCK

REFERENCE

CLOCK

MCR[7] = 1

XTAL2

BAUD RATE

GENERATOR

LOGIC

PRESCALER

LOGIC

(DIVIDE-BY-4)

002aaa233

Fig 12. Prescaler and baud rate generator block diagram.

DLL and DLH must be written to in order to program the baud rate. DLL and DLH are

the least signi铿乧ant and most signi铿乧ant byte of the baud rate divisor. If DLL and DLH

are both zero, the UART is effectively disabled, as no baud clock will be generated.

Remark:

The programmable baud rate generator is provided to select both the

transmit and receive clock rates.

Table 7

and

Table 8

show the baud rate and divisor correlation for crystal with

frequency 1.8432 MHz and 3.072 MHz, respectively.

Figure 13

shows the crystal clock circuit reference.

9397 750 11618

漏 Koninklijke Philips Electronics N.V. 2003. All rights reserved.

Product data

Rev. 04 鈥?19 June 2003

18 of 49